Hello

I wonder about the settings on the code below in keyfobdemo project in Hal_key.c file.

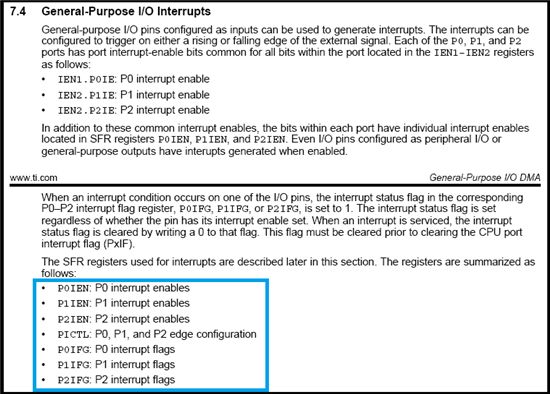

On keyfob demo the Left & Right keys are on P1_0 & P1_1 respectively. What I dont understand is why "HAL_KEY_SW_1_IENBIT" or "HAL_KEY_SW_2_IENBIT" are set to Bit 6? This maybe rudimentary but I find it puzzling.

#define HAL_KEY_SW_1_IEN IEN1 /* CPU interrupt mask register */ #define HAL_KEY_SW_1_ICTL P0IEN /* Port Interrupt Control register */ #define HAL_KEY_SW_1_ICTLBIT BV(0) /* P0IEN - P0.0 enable/disable bit */ #define HAL_KEY_SW_1_IENBIT BV(5) /* Mask bit for all of Port_0 */ #define HAL_KEY_SW_1_PXIFG P0IFG /* Interrupt flag at source */ #define HAL_KEY_SW_2_IEN IEN1 /* CPU interrupt mask register */ #define HAL_KEY_SW_2_ICTL P0IEN /* Port Interrupt Control register */ #define HAL_KEY_SW_2_ICTLBIT BV(1) /* P0IEN - P0.1 enable/disable bit */ #define HAL_KEY_SW_2_IENBIT BV(5) /* Mask bit for all of Port_0 */ #define HAL_KEY_SW_2_PXIFG P0IFG /* Interrupt flag at source */

thanks in advance,

~LD