Hello,

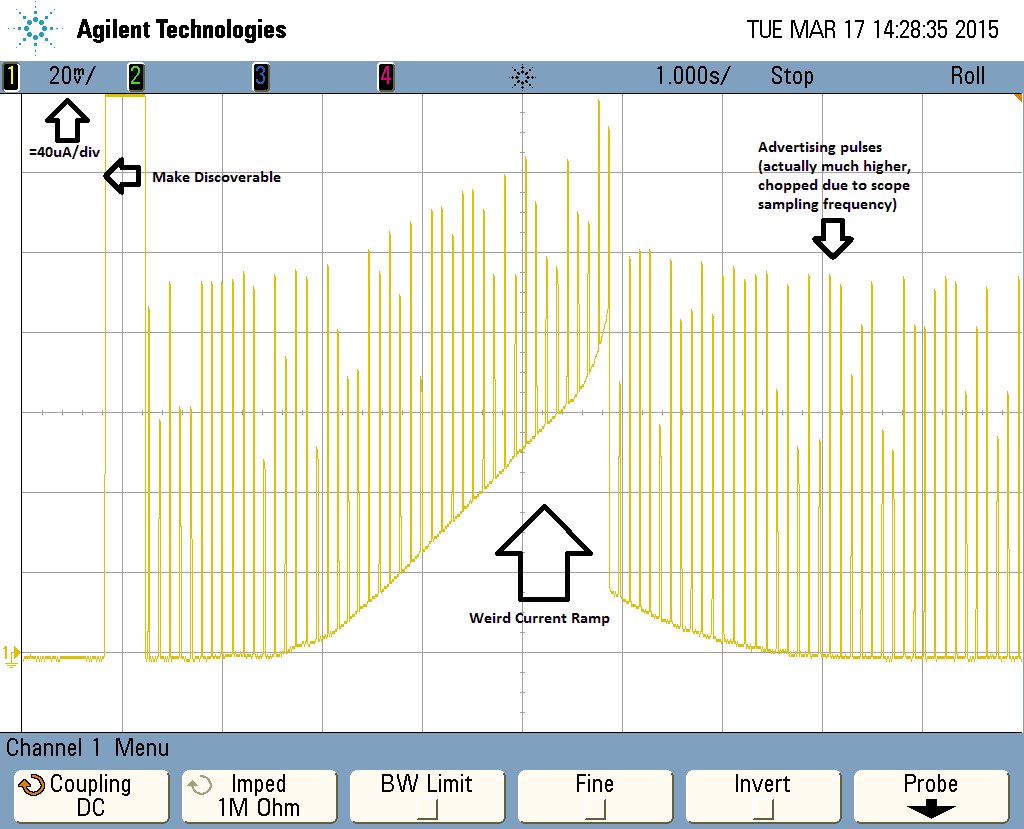

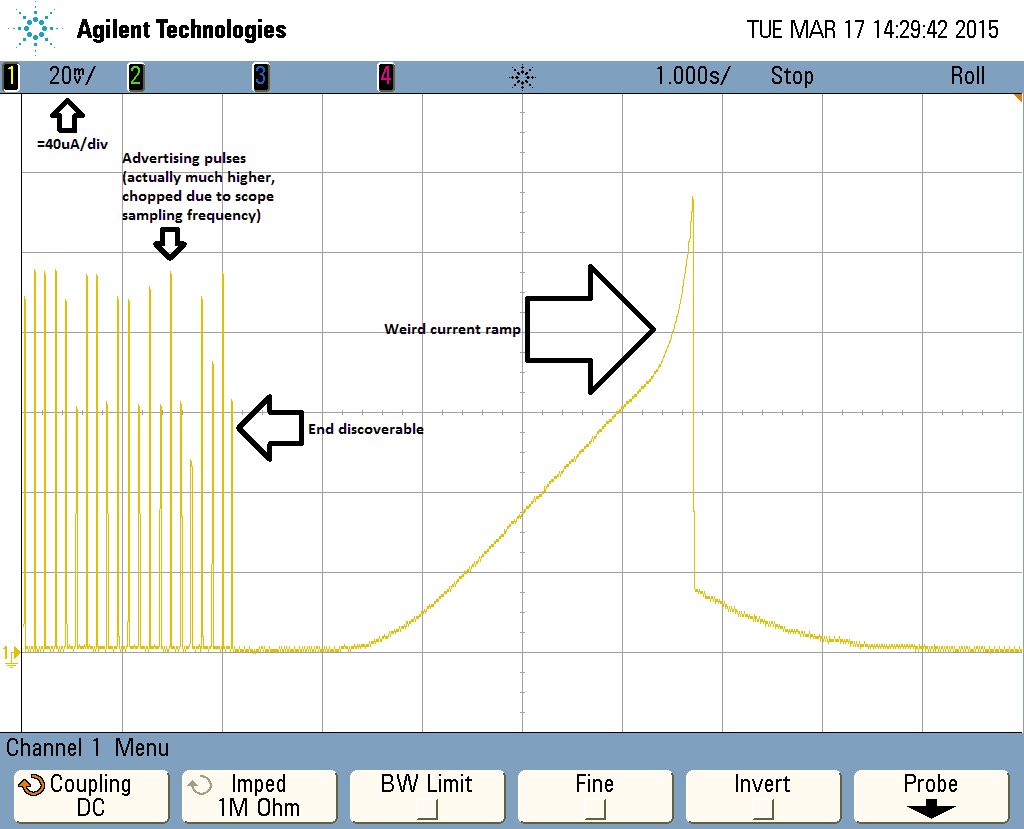

I'm using a CC2541 as SPI Network Processor (HostTestApp) in connectable peripheral mode with Power Savings and the GATT DB off chip. I notice that when ever I send the GAP Make Discoverable command that the CC appears to stay in active mode for 400ms even if I send the End Discoverable and get the responses before that time expired. Advertising, however seems to stop immediately with the End Discoverable.

I assume this is just a delay to prevent running off the sleep timer until the 32Khz crystal is started. I am assuming this as I noticed there is an extension command to tweak this time.

- Is this assumption correct?

- Why isn't the crystal shut down and delay canceled immediately after the End Discoverable?

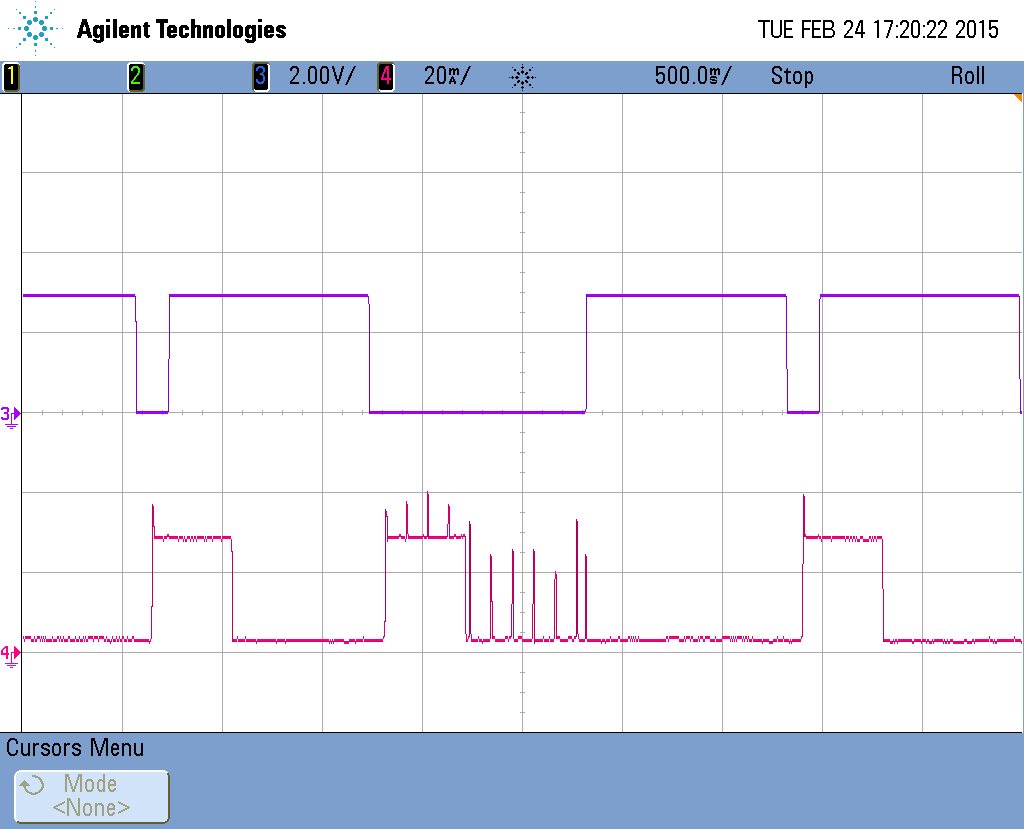

In the scope trace below, violet is low at the initiation of the Make Discoverable and high at the End Discoverable. Red is a 3X current probe.

I am asking these questions because our device has modes where we have very limited power available and need to ensure the CC is in deep sleep before entering these modes. We had previously thought that ending discovery or terminating links and waiting a few tens of milliseconds would do the trick, but it seems we have encountered some cases like this where additional waiting is necessary.

- Are there any other cases where terminating discovery or the connection does not put the CC back in deep sleep (immediately)?

- Are there any other cases where the CC isn't in deep sleep between advertising/connection events?

- If so, can they be identified so we can anticipate and handle them properly?

Thanks in advance,

Nathan