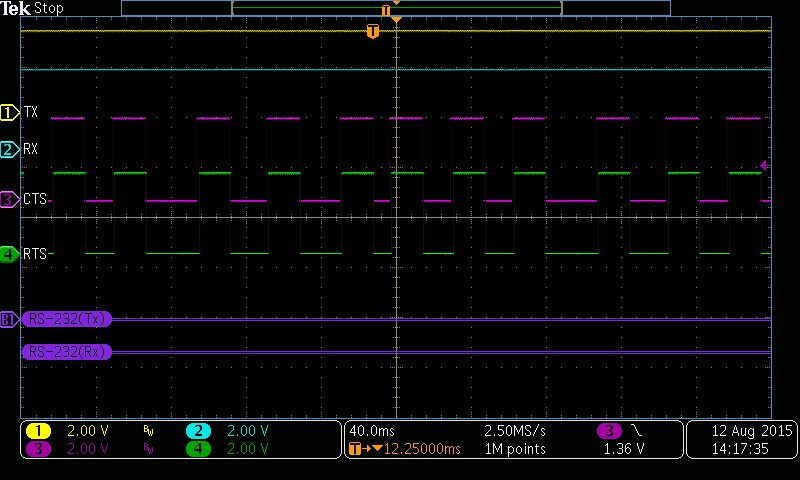

We're accessing an MCU from our CC2540 via UART. The MCU is a Hycon Tech part HY11P23. We've defined a Comm API between the parts, but the HY11P23 is basically a black box to us. We notice that the CTS & RTS lines are constantly active (shown below) even though we are rarely communicating across the Tx & Rx. We understood that our RTS line would go high only at such time as the buffer is full, which never happens. Can someone please explain why we're seeing this correlated RTS & CTS traffic.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.