I'm trying to port the two wire uNPI example with the software handshake from ble sdk 210 repository to work on a CC2650<->STM32F4 setup.

The cc2650 has the simple NP project as is (for 4x4mm cc2650 package). The STM32F4 has RTOS and drivers adaptations.

I'm puzzled on why I'm failing to get the handshake presented on the repository's readme.

The readme showed the following timeline:

SNP: 0x55

SAP: 0x55

SNP: NPI frame

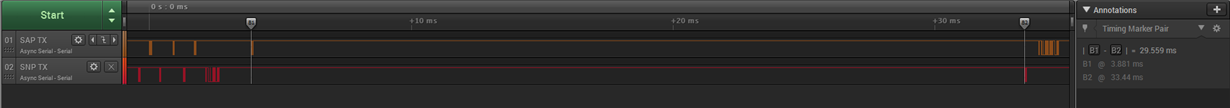

However, my trace looks like the following (the TX part):

SNP: 0x55

SAP: (opening TL; opening UART) 0x55

SNP: 0x55

SAP: 0xFA

SNP: 0xFA

SAP: 0x55

SNP: 0x55

SAP: (closing UART; closing TL)

SNP: NPI frame (power up indication)

because the SAP closed the UART channel, it can't receive the NPI frame.

Where could this problem come from?

- I don't understand why the SNP sent the second chirp after the chrip from the SAP

- I don't understand why the SAP closed the NPI TL after the second chirp (it thought it's the initiator and had nothing to transmit)

I'll appreciate any help.

Best regards,

Gregory