Dear TI Team,

We developed a custom board using the CC2640 microcontroller.

We started using the last BLE-Stack (Version 2.2.0) and the HID Advanced Remote project in IAR IDE 7.70.1.

The major software features are already finished without any problem.

The debug process has been made by SmartRF06 EB but we also have the Debugger DevPack.

Meanwhile, in order to allow upgrade the firmware OTA, the 'Over-the-Air Download User's Guide for BLE-Stack Version 2.2.0' has been strictly followed as guide.

The board has an external flash (Macronix MX25V2006E), connected via SPI interface. Before proceed to the OAD feature addition, the SPI and ExtFlash drivers were added to the project. The driver was adapted to fit in our hardware. As can be seen in the following illustration, the SPI master (CC2640) and the SPI slave (MX25V2006E) are communicating as expected: the master successfully reads the flash information (manufacturer 0xC2 and device ID 0x12). So the hardware and the driver are both well functioning.

// Board LED defines #define BSP_IOID_LED_1 IOID_UNUSED #define BSP_IOID_LED_2 IOID_UNUSED // Board key defines #define BSP_IOID_KEY_LEFT IOID_UNUSED #define BSP_IOID_KEY_RIGHT IOID_UNUSED // Board external flash defines #define BSP_IOID_FLASH_CS IOID_30 #define BSP_SPI_MOSI IOID_19 #define BSP_SPI_MISO IOID_18 #define BSP_SPI_CLK_FLASH IOID_17

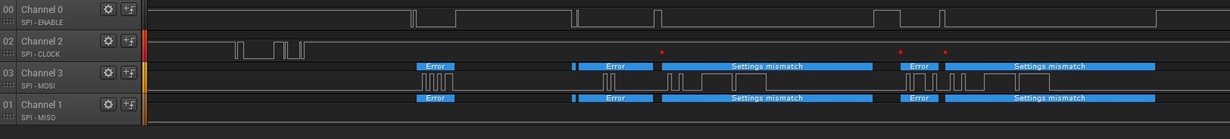

One more time, in order to evaluate the SPI communication, we put some breakpoints to debug the extFlashOpen function. Unfortunately the results are not the expected. The CC2640 can't read the flash information. However it's completely normal because according to the logic analyzer (see picture below), there is no clock signal. The SPI interface configuration remains unchanged:

/* SPI configuration */

SSIIntDisable(BLS_SPI_BASE, SSI_RXOR | SSI_RXFF | SSI_RXTO | SSI_TXFF);

SSIIntClear(BLS_SPI_BASE, SSI_RXOR | SSI_RXTO);

ROM_SSIConfigSetExpClk(BLS_SPI_BASE,

BLS_CPU_FREQ, /* CPU rate */

SSI_FRF_MOTO_MODE_0, /* frame format */

SSI_MODE_MASTER, /* mode */

bitRate, /* bit rate */

8); /* data size */

ROM_IOCPinTypeSsiMaster(BLS_SPI_BASE, BSP_SPI_MISO, BSP_SPI_MOSI,

IOID_UNUSED /* csn */, clkPin);

SSIEnable(BLS_SPI_BASE);

{

/* Get read of residual data from SSI port */

uint32_t buf;

while (SSIDataGetNonBlocking(BLS_SPI_BASE, &buf));

}

Let me just notify that the bit rate is 1 MHz, exactly the same frequency used in the project mentioned above.

What can be the problem? Is there any pin configuration missing?