Other Parts Discussed in Thread: CC2640

Dear Experts,

I have a question regarding the behavior of the bootloader.

We are using the SPI interface to communicate with the bootloader. We are sending a command and then send 0x00 until the CC2640 sends a non-zero response: 0xCC (ACK) or 0x33 (NAK).

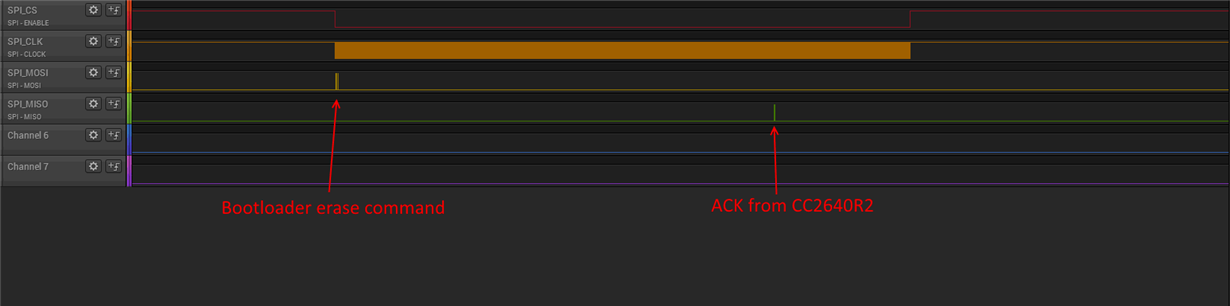

This procedure has worked well on CC2640 R1:

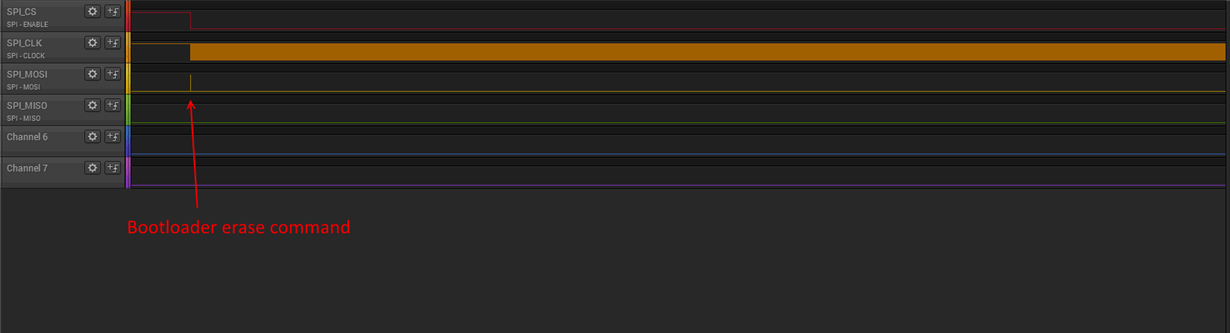

But it failed with R2 (the chip did not send any reply):

We do not know why the two chips R1 and R2 behave differently but we found out, that if we increase the timing between two reads while waiting for ACK/NAK it is working.

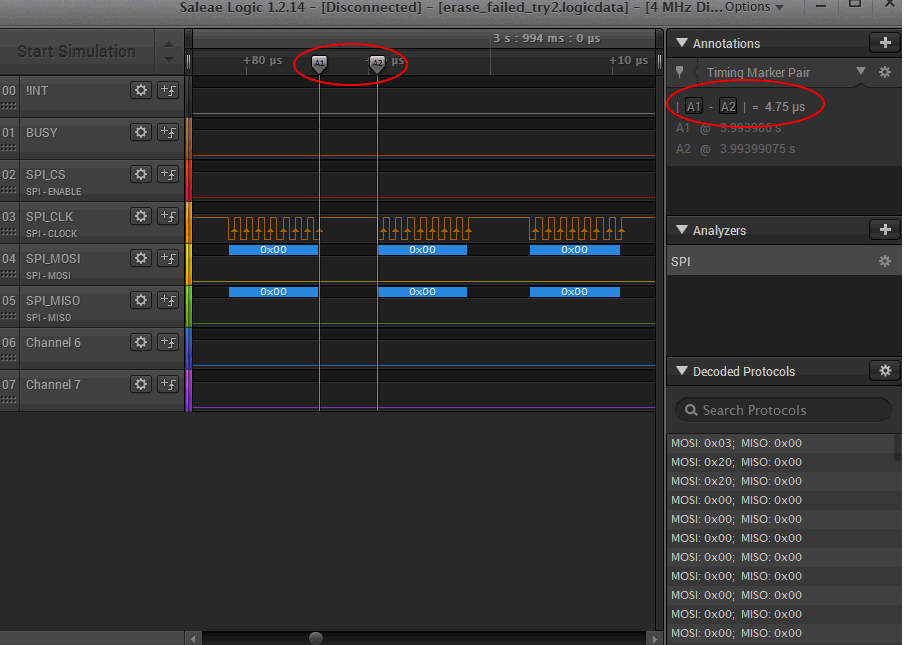

Before, the timeout was around 5us:

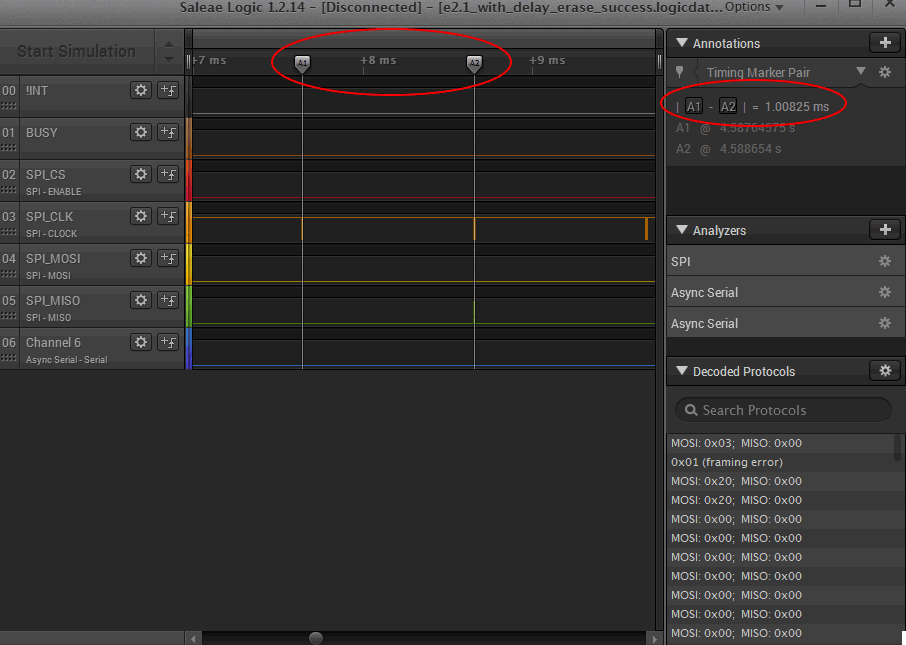

We increased the time to 1ms:

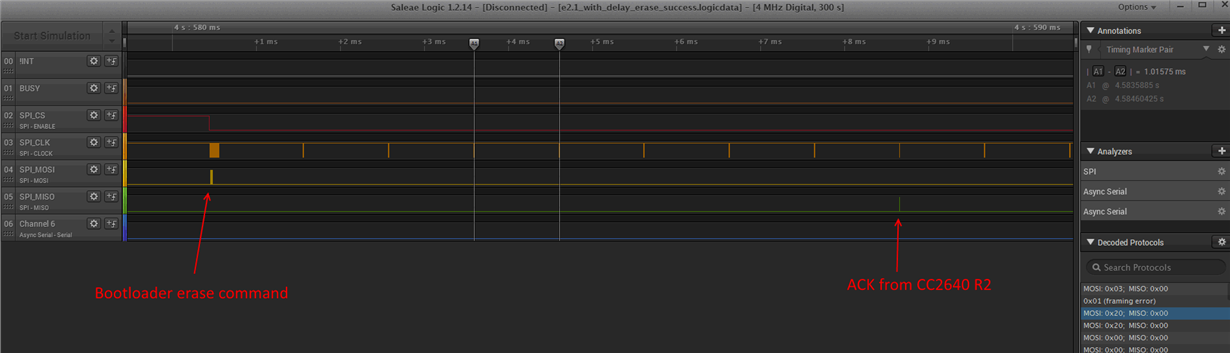

And then the R2 chip did reply to the erase command:

Our assumption is that the frequent SPI interrupts caused by reading 0x00 somehow blocks the chip from performing a proper flash erase. We did not find any restriction regarding this in the TRM or anywhere else.

Thus the question:

What is the suggested time delay for reading the ACK/NAK from the chip?

Is 1 ms ok, or should we increase it? It seems to be working like this but this value is just a random value which we thought would be ok.

Thanks and best regards,

Greg