Other Parts Discussed in Thread: BLE-STACK, CC2640R2F

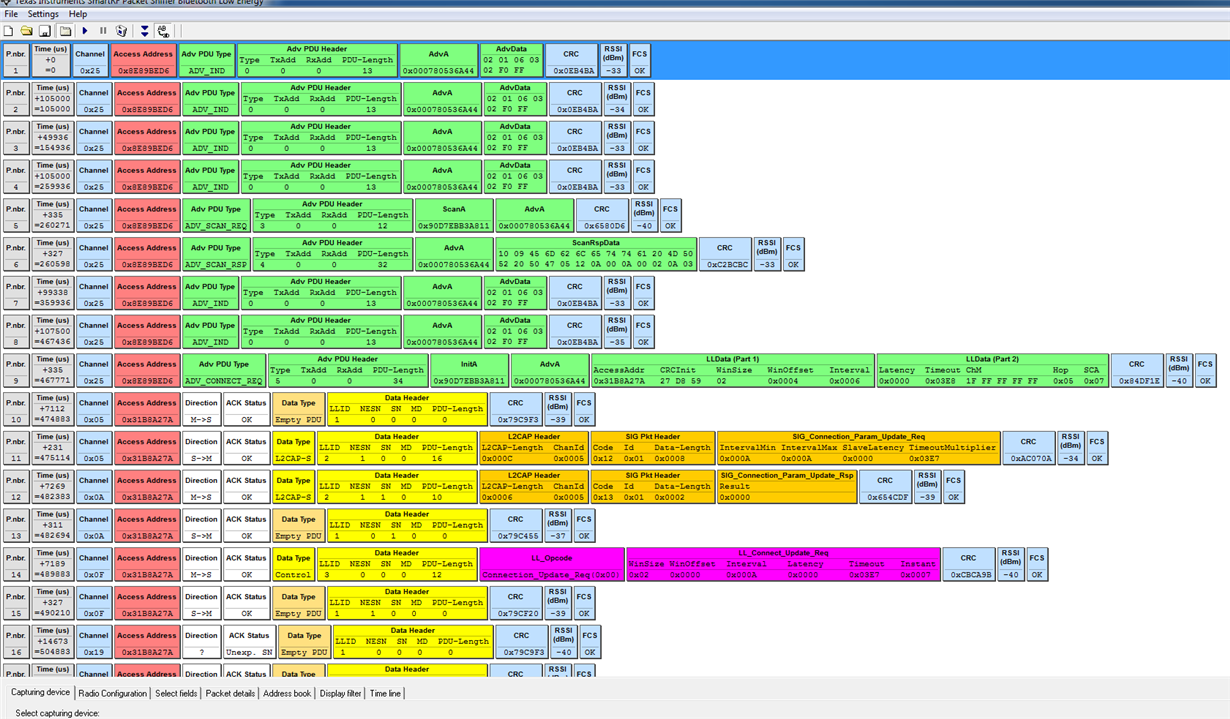

I have a system that is using two CC2540 (BLE112).

One is setup as as a Host (based on HostTestApp) (Master), BLE-STACK 1.2.1

The second as a Peripheral (Slave), BLE-STACK 1.2.1

I periodically miss response packets (with or without data) on the Master side.

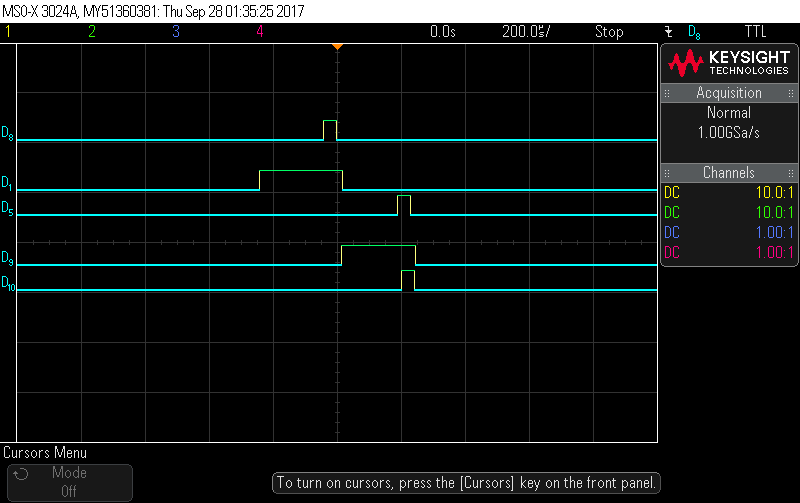

Following is a proper response:

D8: Master RFC_OBS_CTRL->0x31 , High from when the access address has been transmitted until end of packet, low otherwise

D1: Slave RFC_OBS_CTRL->0xAA, RX_active

D5: Slave RFC_OBS_CTRL->0x31, High from when the access address has been transmitted until end of packet, low otherwise

D9: Master RFC_OBS_CTRL->0xAA, RX_active

D10: Master RFC_OBS_CTRL->0x30, High from when receiver has found access address until packet is finished, low otherwise

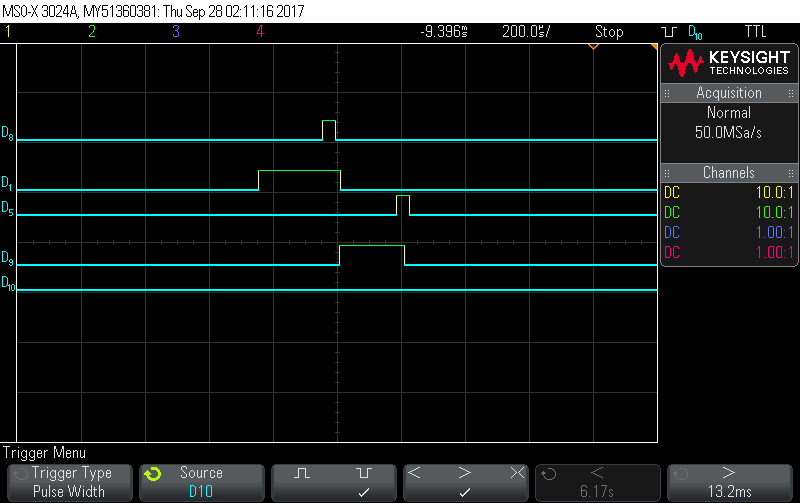

My failure occurs when the Master misses the Response from the Slave. The Masters RX_Active does not capture the the Slaves packet.

D9 should have extended the RX_active to capture the Slaves package D5.

Though sometimes, the D5 Timing completely misses the Masters RX_Active window.

So, what can I do to identify the cause?

What variable can I adjust to extend the RX_Active window, or shift it.

Added notes:

This glitch even occurs when the connection has no data passing back and forth. So the processor is not taxed by other variables.