Part Number: LAUNCHXL-CC2650

Other Parts Discussed in Thread: CC2650

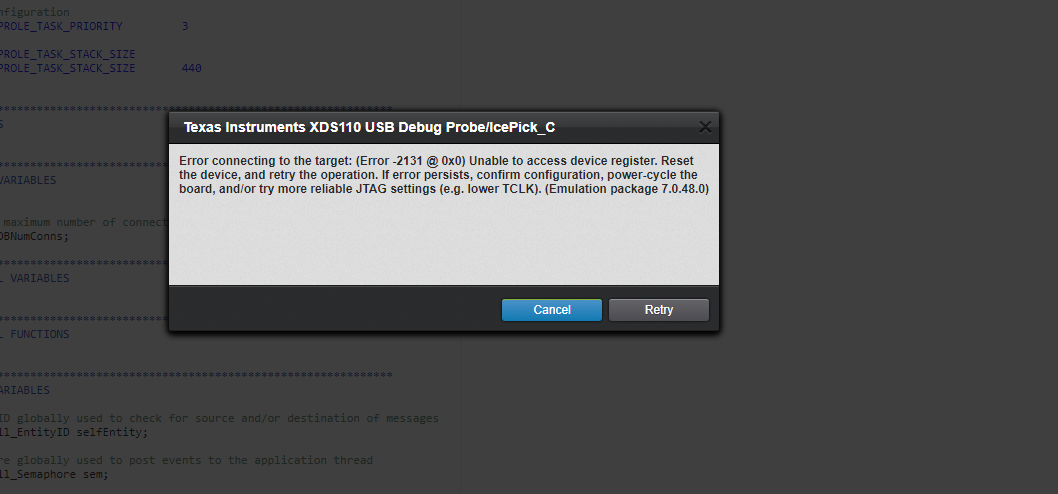

Hello, i'm create CC2650 Custom Board, I try Example program Project Zero, at the first flash CC2650 is Succesfully, but the second Flash, CC2650 Not Detected and cannot Flash Again, what wrong about my Custom Board??