Other Parts Discussed in Thread: CC2564

Hello there.

If we configure the CC2564MODN Codec's "Channel 1 or 2 data out size" to be 24-bits, how does the CC2564MODN handle this when using Dual SCO CSVD 8kHz, 16-bit audio channels? Would it extend the 16-bit data? How would it interpret the 24-bit audio data the Codec is sending it?

Is it possible for the CC2564MODN is support left justified TDM protocol? Even with a configured "Channel 1 data out offset" of 0, it still waits one clock cycle after FSYNC before outputting audio.

We've been using the CC2564MODN in a dual SCO headset product for some time now, but the I2S configuration has never made much sense - and lately some timing issues have arisen that are corrupting the second audio stream at times. I'd like to get this sorted out before tackling it as a Bluetooth or Stack issue.

I've been using the documentation here to guide my tweaking on the CC2564 side: http://processors.wiki.ti.com/index.php/CC256x_VS_HCI_Commands#HCI_VS_Write_CODEC_Config_.280xFD06.29

Our first attempt has the CC2564 as the I2S master. WBS is disabled, RoleNegotiation is disabled and we are forcing a RoleChange to ensure the CC2564 is the SCO master. Audio is 8khZ, 16-bit CVSD and the CODEC is setup default per the HFDemo code. We can have a phone and another Bluetooth device connected and stream dual audio most of the time today.

To address some of the I2S timing issues that seem to occasionally corrupt the second Audio stream in one direction, I've tried making the ADAU1772 the I2S master. But it just refuses to produce 16-bit audio data (I'm working with ADI to troubleshoot this). So, a quick workaround might be to get the CC2564 into 24-bit mode so they play nice.

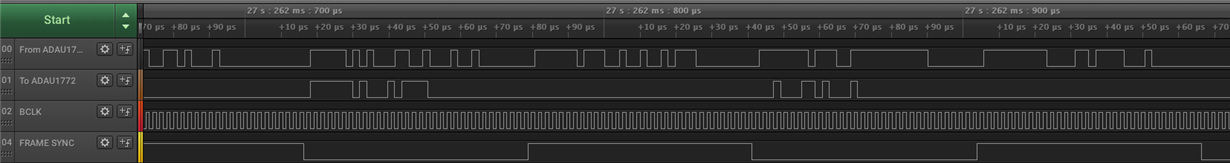

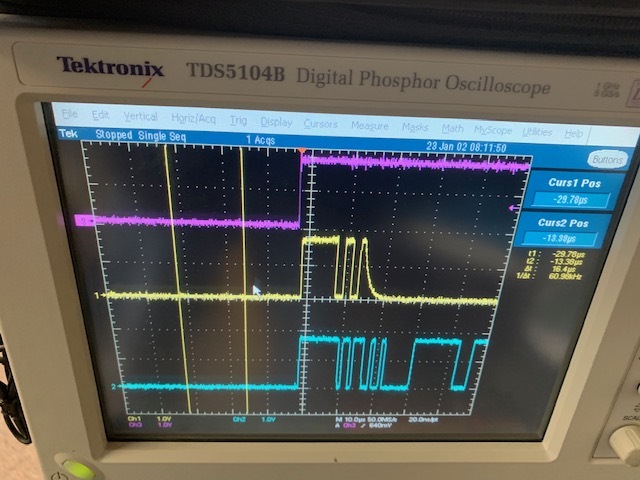

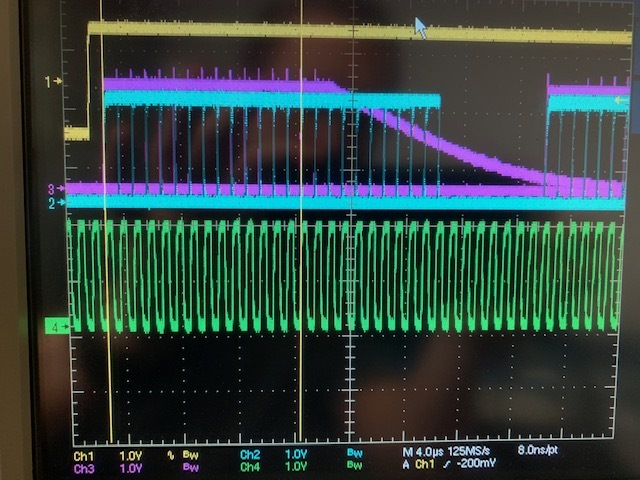

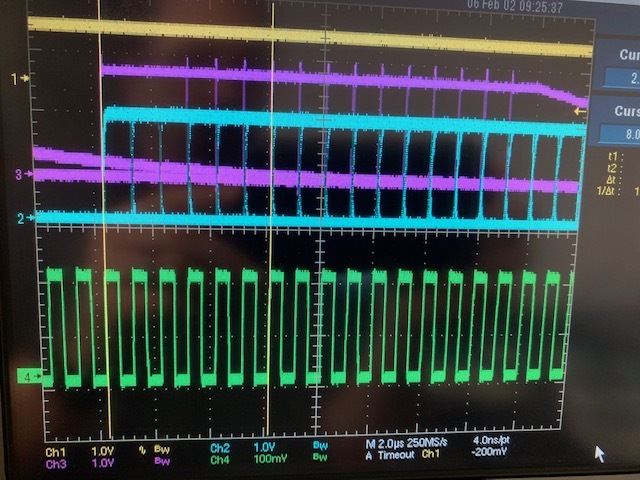

This is a logic analyzer capture of the current interface with an ADI ADAU1772 connected to the CC2564MODN showing the data mismatch.

Thanks!

- Jason