Other Parts Discussed in Thread: CC2640, , CC2544

Hi team,

Our customer use CC2640R2 to connect I2C slave device. Sometimes, CC2640R2 I2C will hang and cannot recovery.

Below show the waveform when i2c transaction fail.

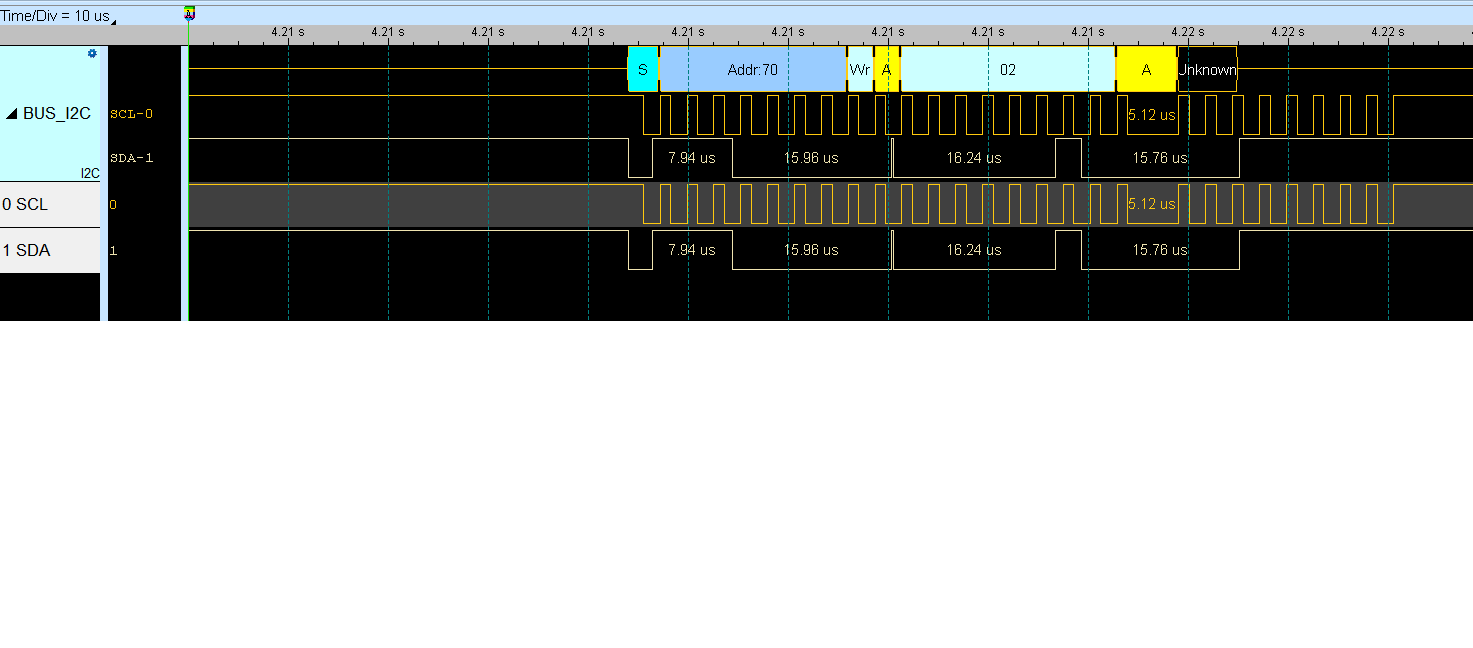

(1) The failure transaction is shown as below.

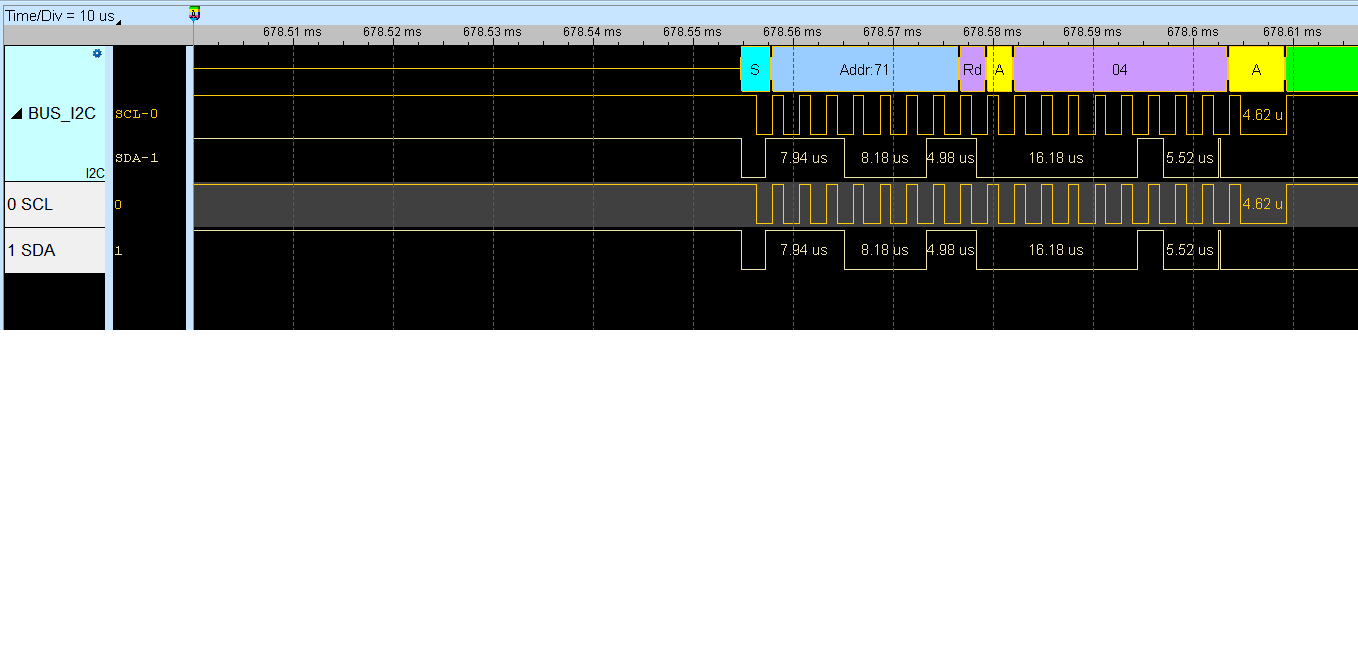

(2) After the i2c transaction failure, cc2640 perform the i2c transfer and the waveform is shown as below.

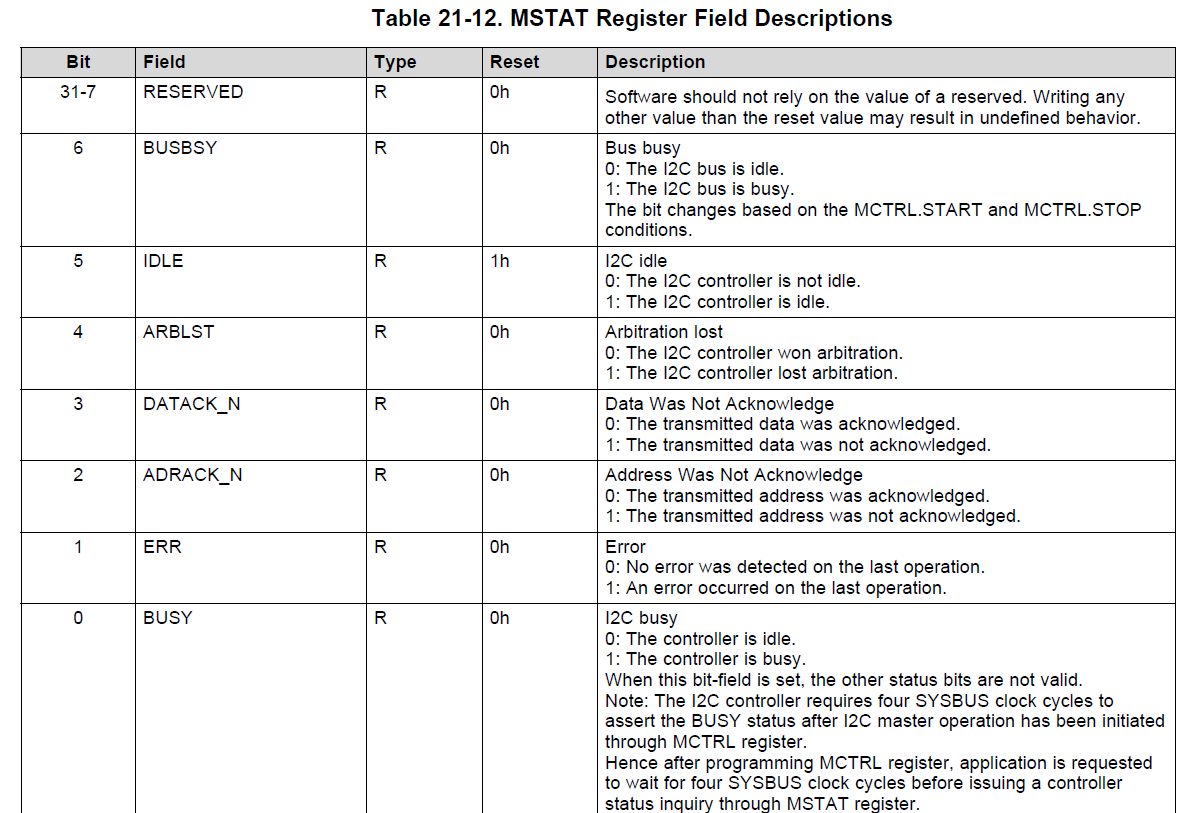

We found the MSTAT register (below Table) and the DATAACK_N bit keep to report 1.

May I know how to clear this bit by setting i2c regisgters? Thanks