Part Number: CC2564MODA

Other Parts Discussed in Thread: , CC256XM4BTBLESW, CC2564

Hi,

I have a customer using CC2564MODA with TM4C129x.

He is evaluating A2DP (not A3DP) demo.

Environments:

CC2564MODAEM

DK-TM4C129X

CC256XM4BTBLESW 1.2R2

CC2564 is successfully connected with smartphone and some data are received from CC2564 to Tiva.

But after SBC_Decode_data() is returned (AudioDecoder.c line#175), all data inside DecodedData.LeftChannelDataPtr and RightPtr are zero.

Customer confirmed the return value of SBC_Decode_data() is SBC_PROCESSING_COMPLETE.

What is possible cause of the issue?

Here are some additional information.

teraterm.txt

SBC buffer contents before SBC_Decode_data() is called.

<DataPtr> 9c,bd,35,7d,00,00,00,00,00,00,00,00,00,77,76,db,6e,ed,b6,db,bb,b6,db,77,6d,b6,dd,dd,b6,db,bb,6d,b6,ee,ed,b6,dd,db,6d,b7,77,6d,b6,ee,db,6d,bb,bb,6d,b7,76,db,6d,dd,db,6d,bb,b6,db,6e,ee,db,6d,dd,b6,db,77,76,db,6e,ed,b6,db,bb,b6,db,77,6d,b6,dd,dd,b6,db,bb,6d,b6,ee,ed,b6,dd,db,6d,b7,77,6d,b6,ee,db,6d,bb,bb,6d,b7,76,db,6d,dd,db,6d,bb,b6,db,6e,ee,db,6d,dd,b6,db,9c,bd,35,7d,00,00,00,00,00,00,00,00,00,77,76,db,6e,ed,b6,db,bb,b6,db,77,6d,b6,dd,dd,b6,db,bb,6d,b6,ee,ed,b6,dd,db,6d,b7,77,6d,b6,ee,db,6d,bb,bb,6d,b7,76,db,6d,dd,db,6d,bb,b6,db,6e,ee,db,6d,dd,b6,db,77,76,db,6e,ed,b6,db,bb,b6,db,77,6d,b6,dd,dd,b6,db,bb,6d,b6,ee,ed,b6,dd,db,6d,b7,77,6d,b6,ee,db,6d,bb,bb,6d,b7,76,db,6d,dd,db,6d,bb,b6,db,6e,ee,db,6d,dd,b6,db,9c,bd,35,7d,00,00,00,00,00,00,00,00,00,77,76,db,6e,ed,b6,db,bb,b6,db,77,6d,b6,dd,dd,b6,db,bb,6d,b6,ee,ed,b6,dd,db,6d,b7,77,6d,b6,ee,db,6d,bb,bb,6d,b7,76,db,6d,dd,db,6d,bb,b6,db,6e,ee,db,6d,dd,b6,db,77,76,db,6e,ed,b6,db,bb,b6,db,77,6d,b6,dd,dd,b6,db,bb,6d,b6,ee,ed,b6,dd,db,6d,b7,77,6d,b6,ee,db,6d,bb,bb,6d,b7,76,db,6d,dd,db,6d,bb,b6,db,6e,ee,db,6d,dd,b6,db,9c,bd,35,7d,00,00,00,00,00,00,00,00,00,77,76,db,6e,ed,b6,db,bb,b6,db,77,6d,b6,dd,dd,b6,db,bb,6d,b6,ee,ed,b6,dd,db,6d,b7,77,6d,b6,ee,db,6d,bb,bb,6d,b7,76,db,6d,dd,db,6d,bb,b6,db,6e,ee,db,6d,dd,b6,db,77,76,db,6e,ed,b6,db,bb,b6,db,77,6d,b6,dd,dd,b6,db,bb,6d,b6,ee,ed,b6,dd,db,6d,b7,77,6d,b6,ee,db,6d,bb,bb,6d,b7,76,db,6d,dd,db,6d,bb,b6,db,6e,ee,db,6d,dd,b6,db,9c,bd,35,7d,00,00,00,00,00,00,00,00,00,77,76,db,6e,ed,b6,db,bb,b6,db,77,6d,b6,dd,dd,b6,db,bb,6d,b6,ee,ed,b6,dd,db,6d,b7,77,6d,b6,ee,db,6d,bb,bb,6d,b7,76,db,6d,dd,db,6d,bb,b6,db,6e,ee,db,6d,dd,b6,db,77,76,db,6e,ed,b6,db,bb,b6,db,77,6d,b6,dd,dd,b6,db,bb,6d,b6,ee,ed,b6,dd,db,6d,b7,77,6d,b6,ee,db,6d,bb,bb,6d,b7,76,db,6d,dd,db,6d,bb,b6,db,6e,ee,db,6d,dd,b6,db,9c,bd,35,7d,00,00,00,00,00,00,00,00,00,77,76,db,6e,ed,b6,db,bb,b6,db,77,6d,b6,dd,dd,b6,db,bb,6d,b6,ee,ed,b6,dd,db,6d,b7,77,6d,b6,ee,db,6d,bb,bb,6d,b7,76,db,6d,dd,db,6d,bb,b6,db,6e,ee,db,6d,dd,b6,db,77,76,db,6e,ed,b6,db,bb,b6,db,77,6d,b6,dd,dd,b6,db,bb,6d,b6,ee,ed,b6,dd,db,6d,b7,77,6d,b6,ee,db,6d,bb,bb,6d,b7,76,db,6d,dd,db,6d,bb,b6,db,6e,ee,db,6d,dd,b6,db,9c,bd,35,7d,00,00,00,00,00,00,00,00,00,77,76,db,6e,ed,b6,db,bb,b6,db,77,6d,b6,dd,dd,b6,db,bb,6d,b6,ee,ed,b6,dd,db,6d,b7,77,6d,b6,ee,db,6d,bb,bb,6d,b7,76,db,6d,dd,db,6d,bb,b6,db,6e,ee,db,6d,dd,b6,db,77,76,db,6e,ed,b6,db,bb,b6,db,77,6d,b6,dd,dd,b6,db,bb,6d,b6,ee,ed,b6,dd,db,6d,b7,77,6d,b6,ee,db,6d,bb,bb,6d,b7,76,db,6d,dd,db,6d,bb,b6,db,6e,ee,db,6d,dd,b6,db,9c,bd,35,7d,00,00,00,00,00,00,00,00,00,77,76,db,6e,ed,b6,db,bb,b6,db,77,6d,b6,dd,dd,b6,db,bb,6d,b6,ee,ed,b6,dd,db,6d,b7,77,6d,b6,ee,db,6d,bb,bb,6d,b7,76,db,6d,dd,db,6d,bb,b6,db,6e,ee,db,6d,dd,b6,db,77,76,db,6e,ed,b6,db,bb,b6,db,77,6d,b6,dd,dd,b6,db,bb,6d,b6,ee,ed,b6,dd,db,6d,b7,77,6d,b6,ee,db,6d,bb,bb,6d,b7,76,db,6d,dd,db,6d,bb,b6,db,6e,ee,db,6d,dd,b6,db,9c,bd,35,7d,00,00,00,00,00,00,00,00,00,77,76,db,6e,ed,b6,db,bb,b6,db,77,6d,b6,dd,dd,b6,db,bb,6d,b6,ee,ed,b6,dd,db,6d,b7,77,6d,b6,ee,db,6d,bb,bb,6d,b7,76,db,6d,dd,db,6d,bb,b6,db,6e,ee,db,6d,dd,b6,db,77,76,db,6e,ed,b6,db,bb,b6,db,77,6d,b6,dd,dd,b6,db,bb,6d,b6,ee,ed,b6,dd,db,6d,b7,77,6d,b6,ee,db,6d,bb,bb,6d,b7,76,db,6d,dd,db,6d,bb,b6,db,6e,ee,db,6d,dd,b6,db,9c,bd,35,7d,00,00,00,00,00,00,00,00,00,77,76,db,6e,ed,b6,db,bb,b6,db,77,6d,b6,dd,dd,b6,db,bb,6d,b6,ee,ed,b6,dd,db,6d,b7,77,6d,b6,ee,db,6d,bb,bb,6d,b7,76,db,6d,dd,db,6d,bb,b6,db,6e,ee,db,6d,dd,b6,db,77,76,db,6e,ed,b6,db,bb,b6,db,77,6d,b6,dd,dd,b6,db,bb,6d,b6,ee,ed,b6,dd,db,6d,b7,77,6d,b6,ee,db,6d,bb,bb,6d,b7,76,db,6d,dd,db,6d,bb,b6,db,6e,ee,db,6d,dd,b6,db,9c,bd,35,7d,00,00,00,00,00,00,00,00,00,77,76,db,6e,ed,b6,db,bb,b6,db,77,6d,b6,dd,dd,b6,db,bb,6d,b6,ee,ed,b6,dd,db,6d,b7,77,6d,b6,ee,db,6d,bb,bb,6d,b7,76,db,6d,dd,db,6d,bb,b6,db,6e,ee,db,6d,dd,b6,db,77,76,db,6e,ed,b6,db,bb,b6,db,77,6d,b6,dd,dd,b6,db,bb,6d,b6,ee,ed,b6,dd,db,6d,b7,77,6d,b6,ee,db,6d,bb,bb,6d,b7,76,db,6d,dd,db,6d,bb,b6,db,6e,ee,db,6d,dd,b6,db,9c,bd,35,7d,00,00,00,00,00,00,00,00,00,77,76,db,6e,ed,b6,db,bb,b6,db,77,6d,b6,dd,dd,b6,db,bb,6d,b6,ee,ed,b6,dd,db,6d,b7,77,6d,b6,ee,db,6d,bb,bb,6d,b7,76,db,6d,dd,db,6d,bb,b6,db,6e,ee,db,6d,dd,b6,db,77,76,db,6e,ed,b6,db,bb,b6,db,77,6d,b6,dd,dd,b6,db,bb,6d,b6,ee,ed,b6,dd,db,6d,b7,77,6d,b6,ee,db,6d,bb,bb,6d,b7,76,db,6d,dd,db,6d,bb,b6,db,6e,ee,db,6d,dd,b6,db,9c,bd,35,7d,00,00,00,00,00,00,00,00,00,77,76,db,6e,ed,b6,db,bb,b6,db,77,6d,b6,dd,dd,b6,db,bb,6d,b6,ee,ed,b6,dd,db,6d,b7,77,6d,b6,ee,db,6d,bb,bb,6d,b7,76,db,6d,dd,db,6d,bb,b6,db,6e,ee,db,6d,dd,b6,db,77,76,db,6e,ed,b6,db,bb,b6,db,77,6d,b6,dd,dd,b6,db,bb,6d,b6,ee,ed,b6,dd,db,6d,b7,77,6d,b6,ee,db,6d,bb,bb,6d,b7,76,db,6d,dd,db,6d,bb,b6,db,6e,ee,db,6d,dd,b6,db,9c,bd,35,7d,00,00,00,00,00,00,00,00,00,77,76,db,6e,ed,b6,db,bb,b6,db,77,6d,b6,dd,dd,b6,db,bb,6d,b6,ee,ed,b6,dd,db,6d,b7,77,6d,b6,ee,db,6d,bb,bb,6d,b7,76,db,6d,dd,db,6d,bb,b6,db,6e,ee,db,6d,dd,b6,db,77,76,db,6e,ed,b6,db,bb,b6,db,77,6d,b6,dd,dd,b6,db,bb,6d,b6,ee,ed,b6,dd,db,6d,b7,77,6d,b6,ee,db,6d,bb,bb,6d,b7,76,db,6d,dd,db,6d,bb,b6,db,6e,ee,db,6d,dd,b6,db,9c,bd,35,7d,00,00,00,00,00,00,00,00,00,77,76,db,6e,ed,b6,db,bb,b6,db,77,6d,b6,dd,dd,b6,db,bb,6d,b6,ee,ed,b6,dd,db,6d,b7,77,6d,b6,ee,db,6d,bb,bb,6d,b7,76,db,6d,dd,db,6d,bb,b6,db,6e,ee,db,6d,dd,b6,db,77,76,db,6e,ed,b6,db,bb,b6,db,77,6d,b6,dd,dd,b6,db,bb,6d,b6,ee,ed,b6,dd,db,6d,b7,77,6d,b6,ee,db,6d,bb,bb,6d,b7,76,db,6d,dd,db,6d,bb,b6,db,6e,ee,db,6d,dd,b6,db,9c,bd,35,7d,00,00,00,00,00,00,00,00,00,77,76,db,6e,ed,b6,db,bb,b6,db,77,6d,b6,dd,dd,b6,db,bb,6d,b6,ee,ed,b6,dd,db,6d,b7,77,6d,b6,ee,db,6d,bb,bb,6d,b7,76,db,6d,dd,db,6d,bb,b6,db,6e,ee,db,6d,dd,b6,db,77,76,db,6e,ed,b6,db,bb,b6,db,77,6d,b6,dd,dd,b6,db,bb,6d,b6,ee,ed,b6,dd,db,6d,b7,77,6d,b6,ee,db,6d,bb,bb,6d,b7,76,db,6d,dd,db,6d,bb,b6,db,6e,ee,db,6d,dd,b6,db, Frame Length : 119 Bit Pool : 53 Bit Rate : 327993 Buffer Length : 128 Frames/GAVD : 16

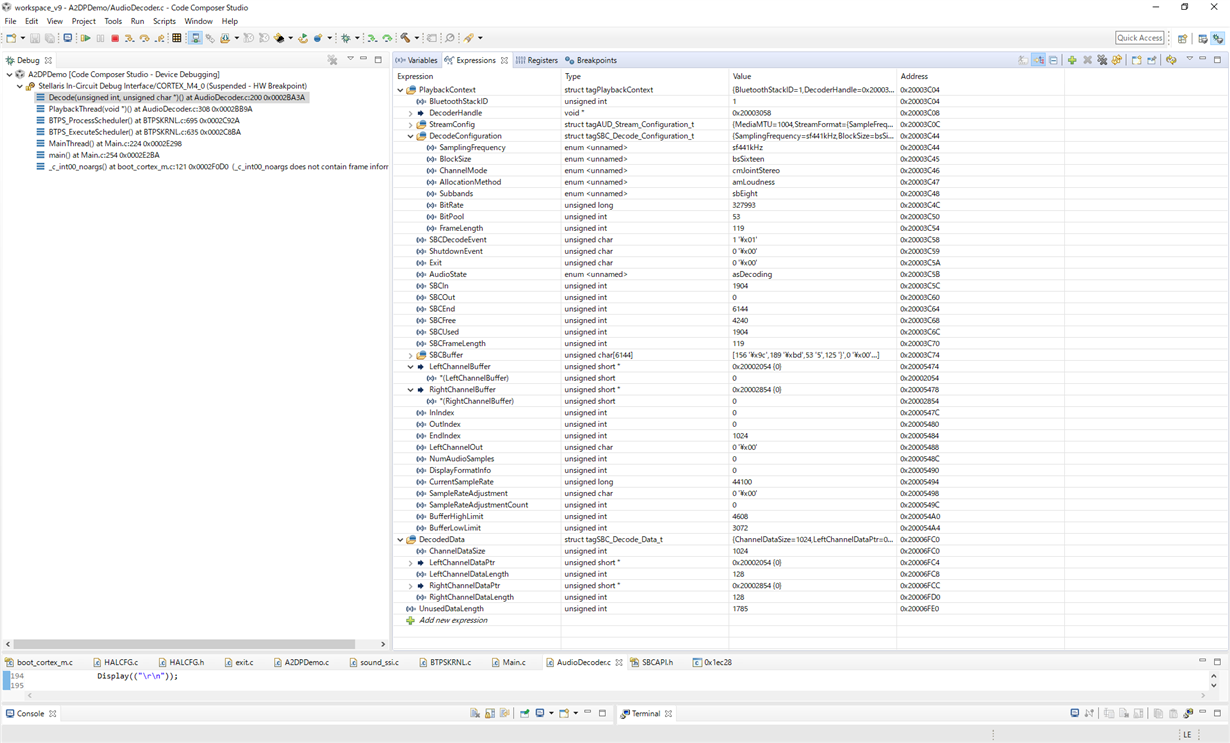

SBC_DECODE_DATA.png

CCS screen shot with parameters just after SBC_Decode_data() is returned.

(this screen shot was taken with different music, so SBC data are different than teraterm.txt)

Thanks and regards,

Koichiro Tashiro