Hi there, I use CC2652P.

In this user manual,

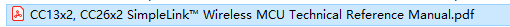

description on SPI clock is this:

PERDMACLK is 48MHz, according to register description, CPSDVSR minimum is 2, SCR minimum is 0, so the maximum clock is 48MHz/[2*(1+0)]=24MHz. (SPI is master mode)

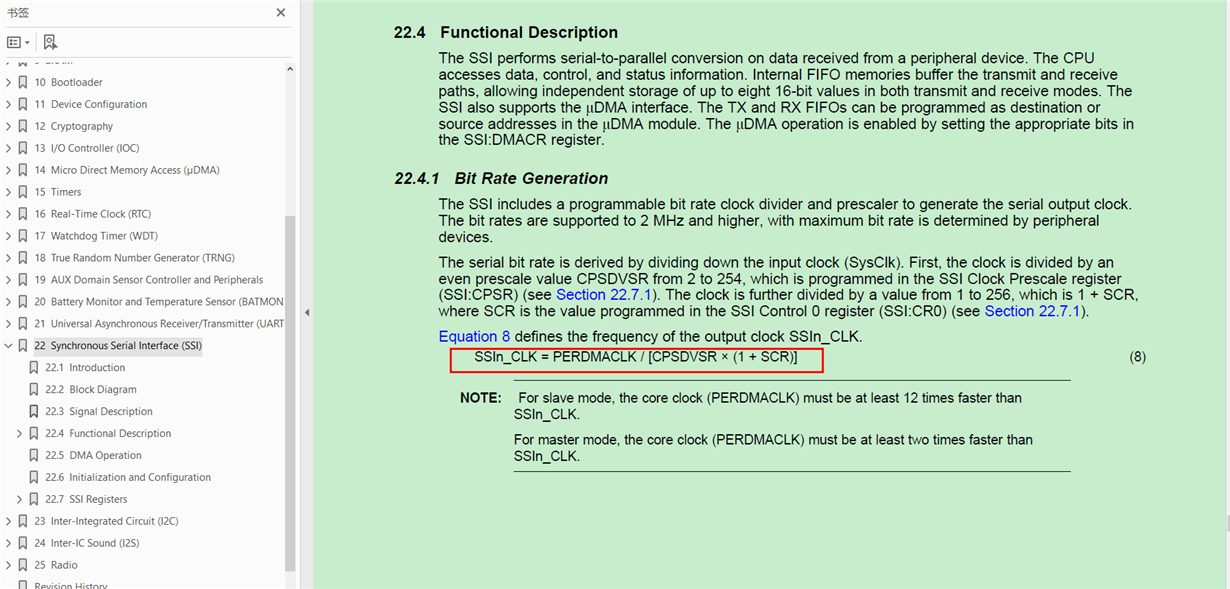

However, according to datasheet, the minimum clk cycle S1 is 12 system clocks. System clock is 48MHz, so maximum spi clock is 48MHz/12 = 4MHz.

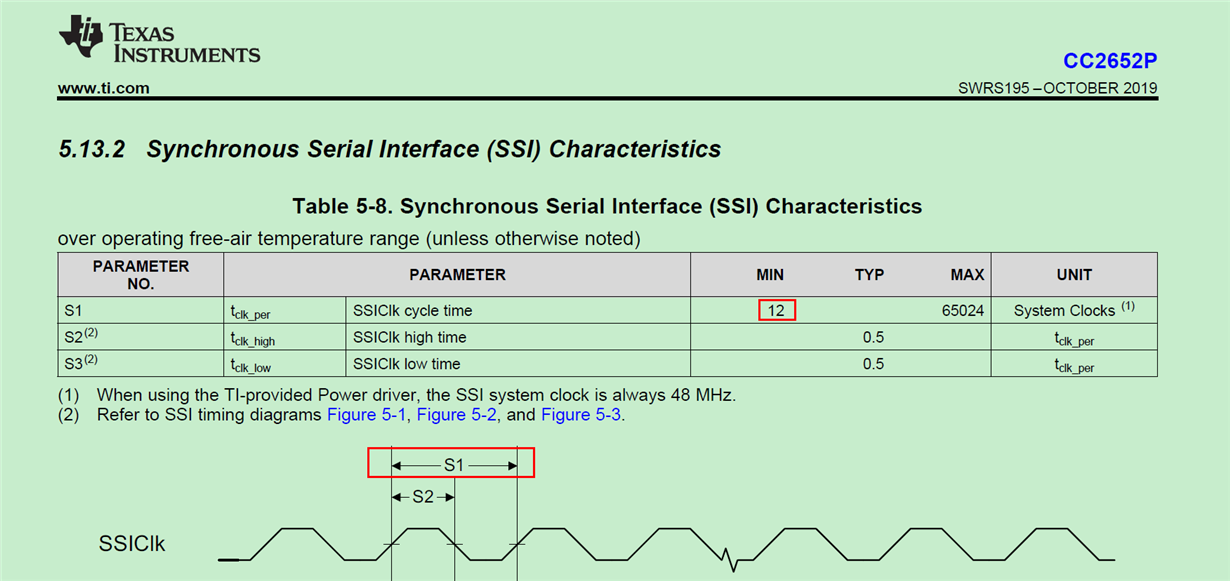

And in another chapter in datasheet, an explicit description tells that the maximum spi clock is 4MHz too.

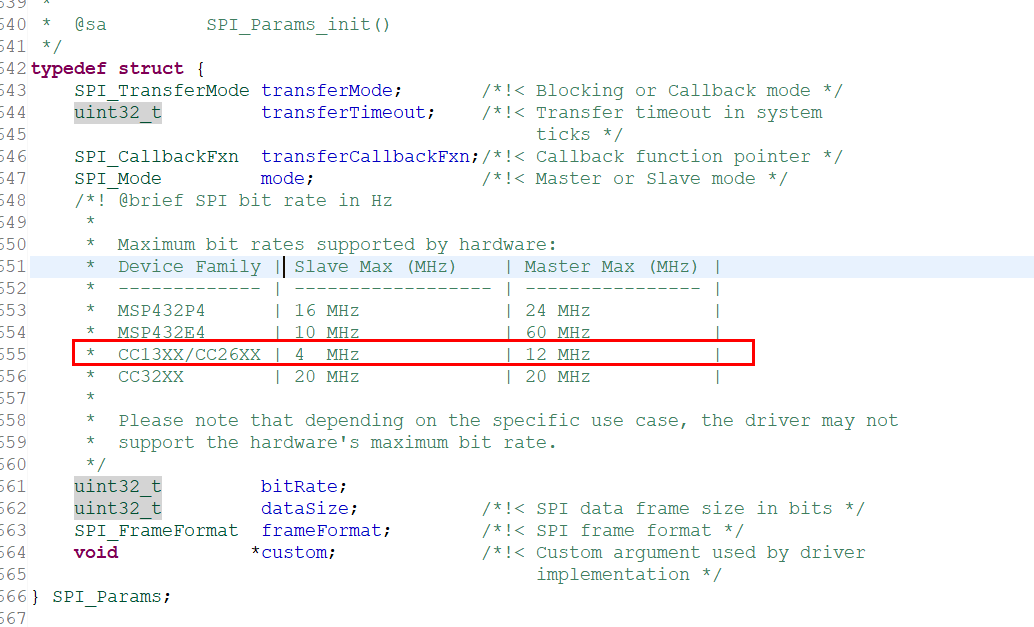

But, in SDK v4.20, another different description again, 12MHz (master mode).

So SPI clock maximum frequency in master mode is :

(1), In Technical Reference Manual, 24MHz;

(2), In datasheet, 4MHz;

(3), In SDK, 12MHz.

I'm confused about this.

What's the real maximum SPI CLK frequency supported by CC2652P in master mode?