Other Parts Discussed in Thread: TRF7970A, TRF7960

Hi Team,

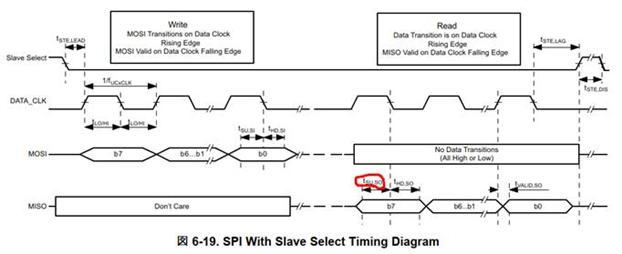

The data sheet of TRF7960A states that Tsu,so goes from the MISO change to the DCLK rise, as shown below. Is this a misleading falling edge? The first bit is also very short.

The data sheet for the TRF7970A was specified with a falling edge.

< The data sheet of TRF7960A : SLOS732G >

< The data sheet of TRF7970A : SLOS743M >

Thanks and Best regards,

Kuerbis