Tool/software:

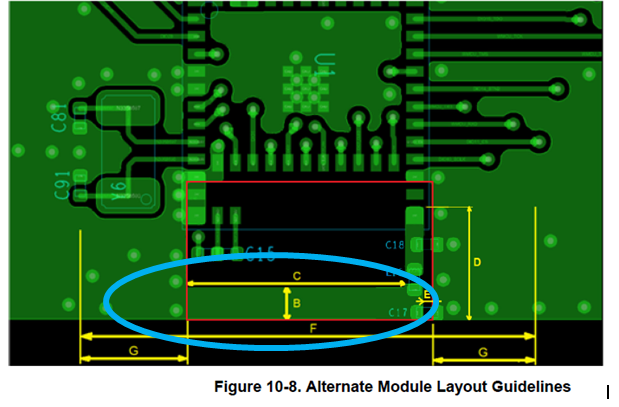

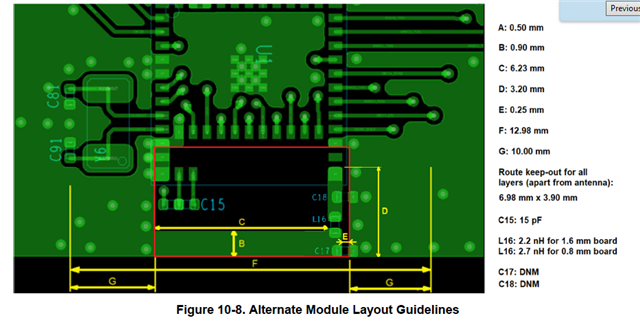

We use the layout guidelines mentioned in the device datasheet. some are reproduced here

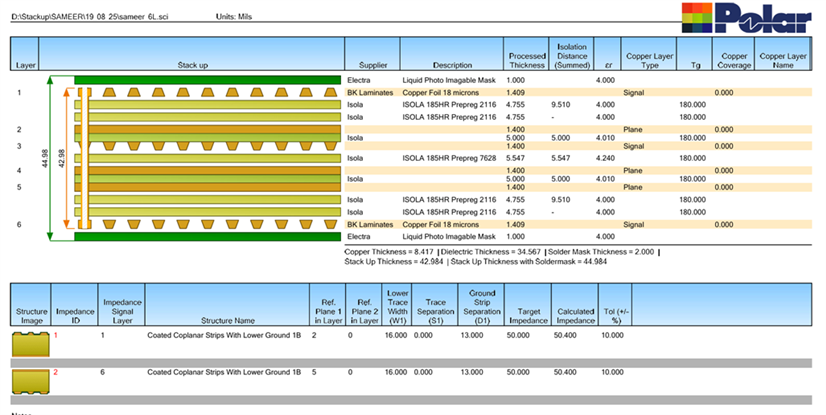

For our layer stackup, the 50 ohm track width is 0.406 mm(16 mils), Whether the above dimension A through

G willm change accordingly, if so what is the values for A through G

thanks