My settings:

////////////////////////////////////////////////////////////////////////////////////////////////////////

halRfWriteReg(CC1120_SYNC2,0xBE);

halRfWriteReg(CC1120_SYNC1,0x9D);

halRfWriteReg(CC1120_SYNC0,0x31);

//halRfWriteReg(CC1120_MODCFG_DEV_E,0x02); // Fdiv = 4 kHz (default)

halRfWriteReg(CC1120_DCFILT_CFG,0x1C);

halRfWriteReg(CC1120_PREAMBLE_CFG1,0x28); // 8 bytes (0xAA)

halRfWriteReg(CC1120_PREAMBLE_CFG0,0x22); // Preamble detection enabled PQT // Start-up Timer=16 symbols // PQT = 2

halRfWriteReg(CC1120_SYNC_CFG1,0x24); // PQT Enable; (max 2 bit error???)

halRfWriteReg(CC1120_SYNC_CFG0,0x11); // 24 bits; < 2 bit error in last received sync byte

halRfWriteReg(CC1120_IQIC,0xC6);

halRfWriteReg(CC1120_CHAN_BW,0x14); // CH filter = 10 eAo

halRfWriteReg(CC1120_MDMCFG0,0x01); // Viterbi detection disabled

halRfWriteReg(CC1120_AGC_REF,0x20);

halRfWriteReg(CC1120_AGC_CS_THR,0x19);

halRfWriteReg(CC1120_AGC_CFG1,0xA9);

halRfWriteReg(CC1120_AGC_CFG0,0xCF);

halRfWriteReg(CC1120_FIFO_CFG,0x00);

halRfWriteReg(CC1120_SETTLING_CFG,0x0E);

halRfWriteReg(CC1120_FS_CFG,0x14); // 410.0 - 480.0 MHz band

halRfWriteReg(CC1120_PKT_CFG1,0x00); // CRC off + disable append mode

halRfWriteReg(CC1120_PKT_CFG0,0x00); // length = CC1120_PKT_LEN

halRfWriteReg(CC1120_PA_CFG2,0x69); // TX power 5 dB

halRfWriteReg(CC1120_PA_CFG0,0x56);

halRfWriteReg(CC1120_IF_MIX_CFG,0x00);

halRfWriteExtReg(CC1120_FREQOFF_CFG,0x22);

halRfWriteExtReg(CC1120_FREQ2,0x6C); // 434 MHz

halRfWriteExtReg(CC1120_FREQ1,0x80);

halRfWriteExtReg(CC1120_FS_DIG1,0x00);

halRfWriteExtReg(CC1120_FS_DIG0,0x5F);

halRfWriteExtReg(CC1120_FS_CAL1,0x40);

halRfWriteExtReg(CC1120_FS_CAL0,0x0E);

halRfWriteExtReg(CC1120_FS_DIVTWO,0x03);

halRfWriteExtReg(CC1120_FS_DSM0,0x33);

halRfWriteExtReg(CC1120_FS_DVC0,0x17);

halRfWriteExtReg(CC1120_FS_PFD,0x50);

halRfWriteExtReg(CC1120_FS_PRE,0x6E);

halRfWriteExtReg(CC1120_FS_REG_DIV_CML,0x14);

halRfWriteExtReg(CC1120_FS_SPARE,0xAC);

halRfWriteExtReg(CC1120_FS_VCO0,0xB4);

halRfWriteExtReg(CC1120_XOSC5,0x0E);

halRfWriteExtReg(CC1120_XOSC1,0x03);

halRfWriteReg(CC1120_PKT_LEN, 12); // Max payload data length

////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

From generator we send the packet (25 dyte) :

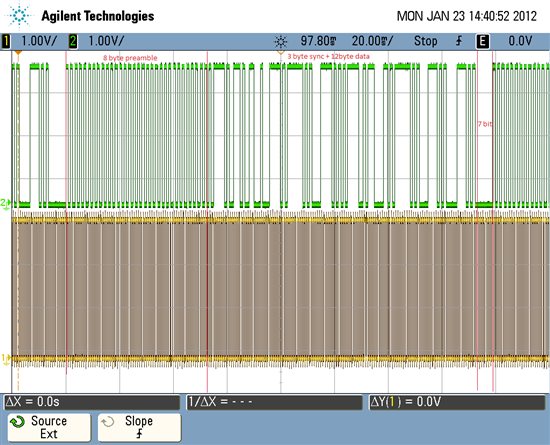

0xAAAAAAAAAAAAAAAA - preamble (8 byte)

0xBE9D31 - our sync (3 byte)

0x1F5FD43EABE5C35FD43D41EA - coding data (12 byte)

0x0000 - 2 byte

CRC disabled - we calculate separately

Result: the received data (12 byte) - correct (0x1F5FD43EABE5C35FD43D41EA)

But, if we send incorrect preamble, for example: 0x8B8B8B8B8B8B8B8B, or even packet: BE9D31 1F5FD43EABE5C35FD43D41EA 0000000000000000 - (25 byte without preamble(0xAA)) - received data (12 byte) - correct (0x1F5FD43EABE5C35FD43D41EA). Though Preamble detection enabled.

Questions:

1) We set - PQT enabled for SYNC and PREAMBLE. SYNC_CFG1.SYNC_THR [4:0] & PREAMBLE_CFG0.PQT [3:0] - set quantity Bit Error (???) and how calculate these values ? Because, if check PQT_SYNC_ERROR we see PQT_ERROR[7:4] = 1111b and SYNC_ERROR[3:0] = 00XXb.

2) SYNC_CFG0.SYNC_NUM_ERROR[1:0] = 0x01 - 2 bit error in all sync word or only in 1 byte SYNC0 ?

3) Earlier we working with ADF, but want use CC1120. Where exactly set admissible bit error for Sync word and Preamble?

4) It is possible on СС1120 to make so:

in TX side we use packet with 64 bits preamble, 24 bit sync and some data, but

on RX side - when received only 24 or 32 bits preamble (with Bit error < 2), we start search - sync word, and when sync word was detected - we get data.

I assume that it can be made so - TX device: config PREAMBLE_CFG1.NUM_PREAMBLE = 8 bytes , and

RX device: config PREAMBLE_CFG1.NUM_PREAMBLE = 3 or 4 bytes ?

5) You can give more information about MDMCFG0.VITERBI_EN ???

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.