Hi,

I have a legacy design which I am changing from CC1020 to the CC1120.

The system consists of a wireless master (Panel) which communicates to several wireless slaves (Devices).

Messages can be exchanged as follows:

Panel can talk to Devices; Devices can talk to the Panel; Devices not allowed to talk to each other.

The nature of the protocol and existing software suggests I use sync. serial mode.

RF setup is 9600 Baud, GFSK @ 868MHz.

Tx mode:

- Tx enabled in synchronous serial mode (Message data is transferred using GPIO's configured as DCLK and DIO).

- CC1120 provides DCLK when Tx carrier is up, external mcu uses this to clock in the preamble followed by sync word and payload.

Rx mode:

- Rx enabled in synchronous serial mode with sync word detection.

- CC1120 only provides DCLK and DIO when it finds a sync word match.

- Dual sync search is used. (0xCCF0 and 0xAAF0).

- Preamble detect is not used as there are two preamble types in use 0xCC , 0xAA.

Devices were converted over to use the CC1120 without issue.

CC1120 to CC1020 comm's works fine both ways.

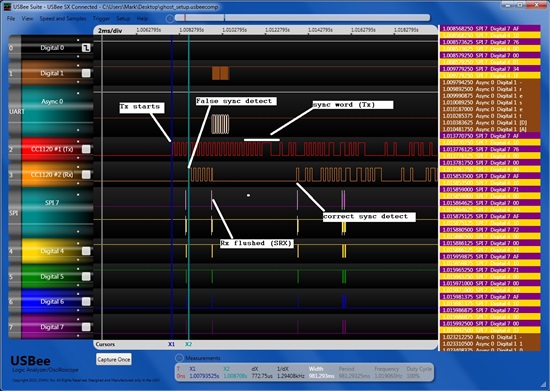

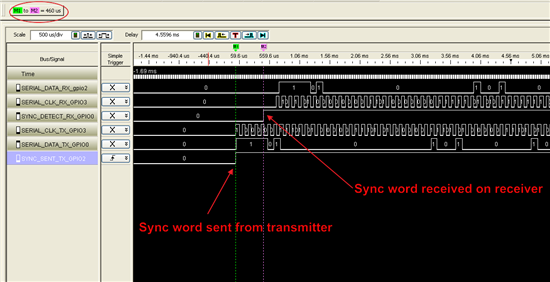

When the Panel was upgraded to use the CC1120 something strange started happening....

- Panel puts its CC1120 in to the rx mode described above (i.e. DCLK and DIO are idle since it is waiting for a sync word match)

- Panel expects that when the CC1120 starts providing DCLK that a sync detect has occured and starts reading in the payload.

Case A:

- When a Device fitted with CC1020 starts transmitting the Panel CC1120 detects a sync word match at the appropriate point and starts providing DCLK and DIO.

- Panel reads in the payload, works fine.

Case B:

- When a Device fitted with CC1120 starts transmitting then Panel CC1120 detects a sync word match within 700us of the transmitting CC1120 providing DCLK (i.e. pretty much as soon as the transmitting device's carrier going up).

- Panel reads in DCLK and DIO thinking it is the payload (when it is actually the preamble).

- Panel rejects this as a mis-formatted message and restarts the search. By which time it has missed the actual message.

- This problem exists both ways Panel Tx >>> Device Rx and Device Tx >>> Panel Rx.

My questions:

- Has anyone seen this false sync word lock when the carrier from another CC1120 goes up?

- Any ideas what I'm doing wrong or how to solve this problem?

Mark.