Hi all !

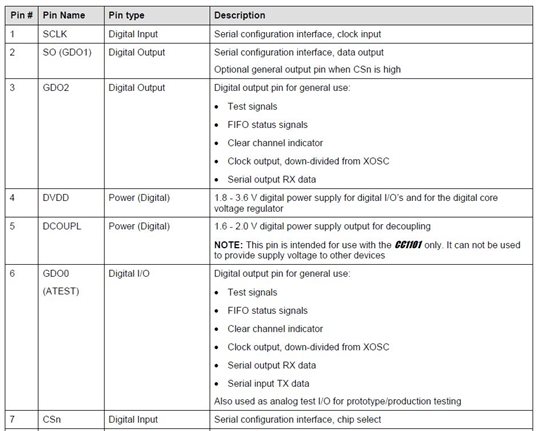

I am trying to interface CC1101 with MSP430F5529 using MSP-EXP430F5529 and CC1101-CC1190EM boards. I have achieved to read and write registers of CC1101, but I can`t use the GDO0 and GDO2 pins as inputs. When I configure them as inputs and with their associated interrupt isr, the SPI doesn´t run: I always read 0x00 and 0xFF. Only when I configure those pins as outputs, the SPI runs well.

What am I doing wrong? Anybody can help me? Has anybody a sample code with those evaluation boards? I test a lots of SPI codes for CC1101 but anyone runs well with MSP-EXP430F5529 board when I try to receive and send packets via Radio to another evaluation board.

Thanks a lot for pay attention!

Some of code that I am using is:

------------------------------------------------------------------------------------------------------------------------------------------------

/*PIN CONFIGURATION*/

/***************

RADIO PIN INTERFACE:

P3.0 -> SIMO SPI

P3.1 -> SOMI SPI

P3.2 -> CLK SPI

P2.6 -> CS radio SPI SLAVE TRANSMIT ENABLE

P2.3 -> PA_EN

P2.4 -> LNA_EN

GD0 -> P2.3

GD2 -> P2.4

***************/

P3SEL |= SPI_MISO + SPI_MCLK + SPI_MOSI;

P2SEL &= ~SPI_CS;

P3DIR |= SPI_MCLK + SPI_MOSI;

P3DIR &= ~SPI_MISO;

P2DIR |= SPI_CS;

P3REN |= SPI_MOSI; //Pull-up enable

P3OUT |= SPI_MOSI;

P2OUT |= SPI_CS; //CS = 1;

//HGM, LNA, PA, GD0 y GD2 PINS

P2SEL &= ~(PA_PIN + GD0_CC1101 + GD2_CC1101);

P2DIR |= PA_PIN; // + GD0_CC1101 + GD2_CC1101; //if I put GD0 and GD2 as inputs, SPI runs

P2DIR &= GD0_CC1101 + GD2_CC1101; //SPI NOT RUNS WITH THIS PINS AS INPUTS

P4SEL &= ~(HGM_PIN + LNA_PIN);

P4DIR |= HGM_PIN + LNA_PIN; //OUTS

------------------------------------------------------------------------------------------------------------------------------------------------

/*SPI CONFIGURATION FOR MSP-EXP430F5529*/

UCB0IE = 0;

UCB0CTL1 |= UCSWRST; // Put state machine in reset

UCB0IFG &= ~(UCRXIFG + UCTXIFG); //Rx & Tx flags clean

UCB0CTL0 = UCCKPL + UCMSB + UCMST + UCMODE_0 + UCSYNC; // 3-pin, 8-bit SPI master // Clock polarity select - The inactive state is high // MSB first

UCB0CTL1 |= UCSSEL__SMCLK; // Use SMCLK, keep RESET

//BDRSPI calculated for 9600bps with FCLK=4MHz

UCB0BR0 = BDRSPI & 0x00FF;

UCB0BR1 = (BDRSPI>>8) & 0x00FF;

UCB0CTL1 &= ~UCSWRST; // Release USCI state machine

UCB0IE |= UCRXIE + UCTXIE;// Tx & Rx SPI interrupt enabled

------------------------------------------------------------------------------------------------------------------------------------------------

/*CHIP SELECT FUNCTIONS*/

void CSn_1 (void)

{

unsigned int wait;

for(wait=500;wait>0;wait--){_nop();}

P2OUT |= SPI_CS; //CS = 1

}

void CSn_0 (void)

{

//SPI_MISO Pin 3.1 of Msp430f5529

P3SEL &= ~SPI_MISO; //Configure SOMI as input

P3DIR &= ~SPI_MISO;

P2OUT &= ~SPI_CS; //CS = 0

while(P3IN & SPI_MISO); //Wait until SOMI go low

P3DIR |= SPI_MISO; //Reconfigure SOMI

P3SEL |= SPI_MISO;

}

------------------------------------------------------------------------------------------------------------------------------------------------

/*SPI Write and Read FUNCTIONS*/

//READ REGISTERS

unsigned char ReadReg(unsigned char addr, unsigned char mode)

{

unsigned char local_addr;

unsigned char read_value;

local_addr = addr | mode;

CSn_0();

while((UCB0STAT & 0x01)); //Wait until SPI not busy

UCB0TXBUF = local_addr; //write register address

while((UCB0STAT & 0x01)); //Wait until SPI not busy

read_value = UCB0RXBUF;

while((UCB0STAT & 0x01)); //Wait until SPI not busy

UCB0TXBUF = 0xFF; //dummy byte

while((UCB0STAT & 0x01)); //Wait until SPI not busy

read_value = UCB0RXBUF; //Register's value

CSn_1();

return read_value;

}

void setreg(unsigned char reg, unsigned char data)

{

CSn_0();

writeByte(reg);

writeByte(data);

CSn_1();

}

------------------------------------------------------------------------------------------------------------------------------------------------

/*INTERRUPTS ISR*/

//SPI RADIO INTERRUPT

#pragma vector=USCI_B0_VECTOR

__interrupt void Radio_RX(void)

{

extern volatile unsigned char read_Byte_SPI;

extern volatile unsigned char flag_byte_receive;

extern volatile unsigned char tx_empty;

switch(UCB0IFG & (SPI_TXIFG + SPI_RXIFG))

{

case 1:

//read_Byte_SPI = UCB0RXBUF;

flag_byte_receive = TRUE;

UCB0IFG &= ~SPI_RXIFG ;

break;

case 2: //Transmision

P1OUT ^= 0x20;

P1OUT ^= 0x10;

tx_empty = TRUE;

//TEST: UCB0IE &= ~UCTXIE;

break;

case 3: //Recepcion

//P1OUT |= 0x08;

//read_Byte_SPI = UCB0RXBUF;

//flag_byte_receive = TRUE;

UCB0IFG &= ~SPI_RXIFG;

break;

default:

break;

}

}

//PORT 2 INTERRUPT

#pragma vector=PORT2_VECTOR

__interrupt void Port2_ISR(void)

{

extern volatile unsigned char dato_recibido;

dato_recibido = 2;

switch(P2IFG)

{

case GD0_CC1101:

if(P2IN & GD0_CC1101)

P1OUT |= 0x20;

else

P1OUT |= 0x10;

dato_recibido = TRUE;

P2IFG = 0;//~GD0_CC1101;

break;

case GD2_CC1101:

P1OUT ^= 0x04;

P2IFG &= ~GD2_CC1101;

break;

default:

break;

}

}