Dear All,

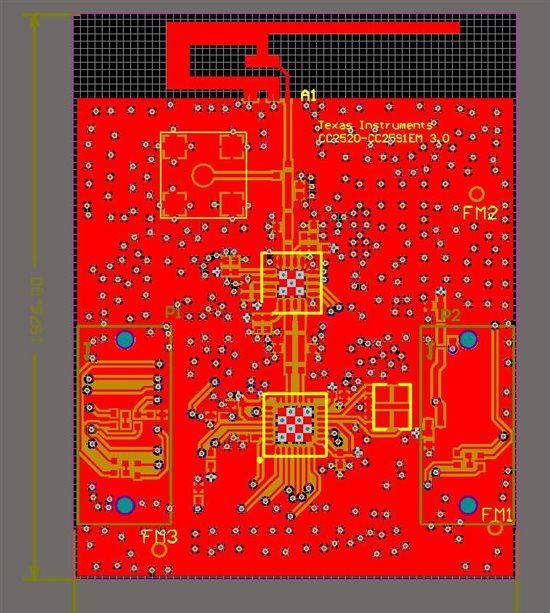

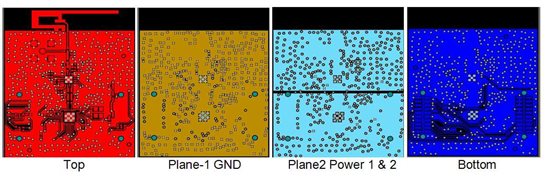

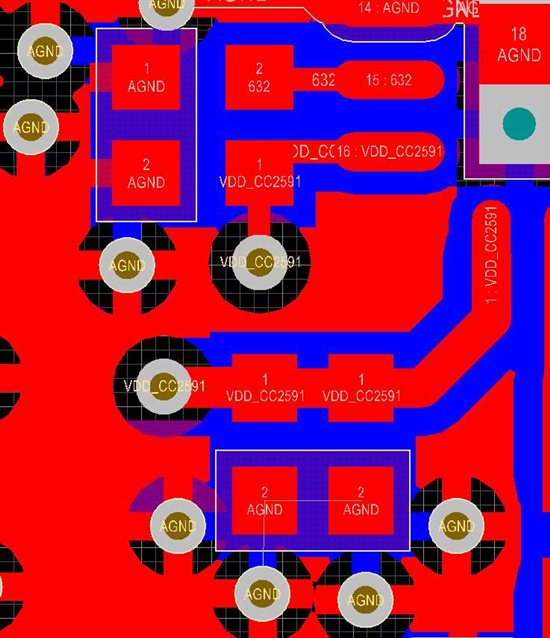

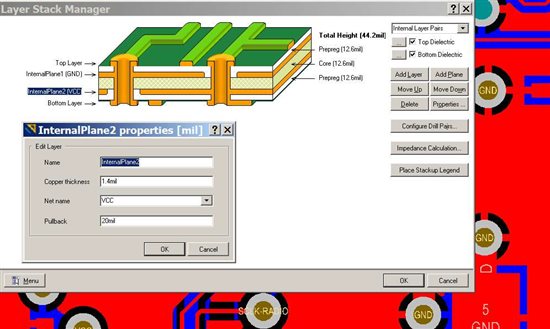

I am having some difficulites understanding the cc2591 design files. No matter what I try, I cannot open the files for editing, only viewing via the latest CADSTAR 11 viewer. How could I edit those, if we do not own a Mentor Graphics editing software? I have Autocad, Protel, Orcad access, but not really worked with the Cadstar or Mentor Graphics software.

Best wishes and a Happy New Year 2010!

Ghasem