Hello!

We are making pcb for BT4 RGB led driver. We already made our first prototype, but BT was not functioning, probably because PCB was only 2 layer 1.6 m thick, so there was no way to provide 50 ohm caracteristic impedance for RF tracks.

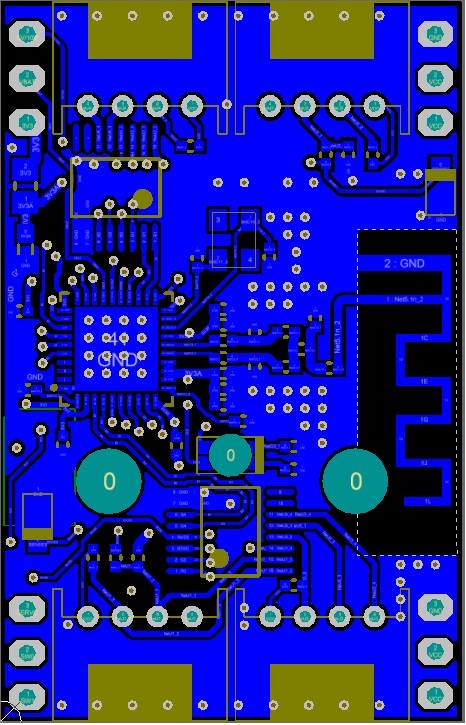

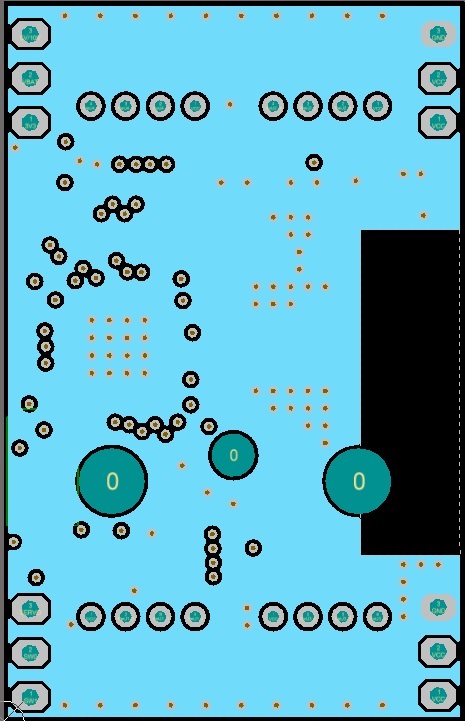

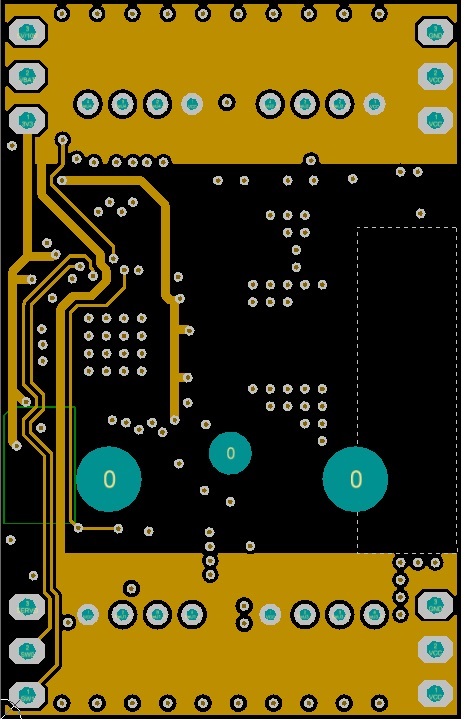

I'm posting image of second revision, which has 4 PCB layers. I would like to hear your comments and if I should correct pcb routing.

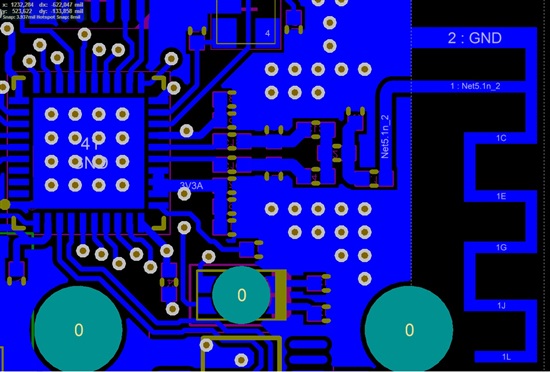

This is top layer, of RF portion of circuit. Underneath ths layer is solid copper pour. Components that form a balun are placed exactly as in reference design (http://processors.wiki.ti.com/index.php/SAT_-_Gas_Sensor_Platform_with_Bluetooth_Low_Energy).

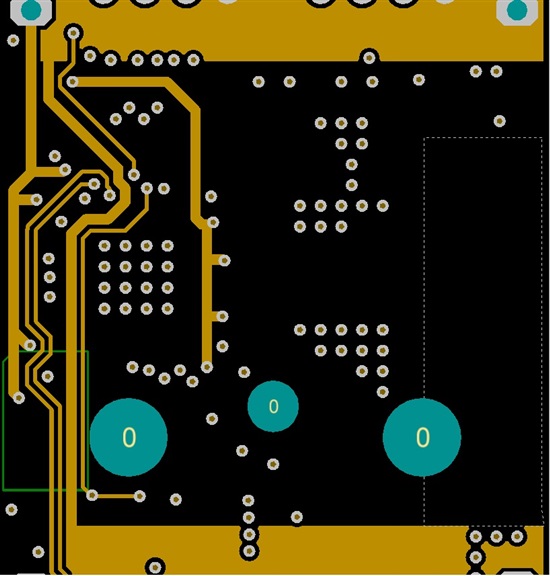

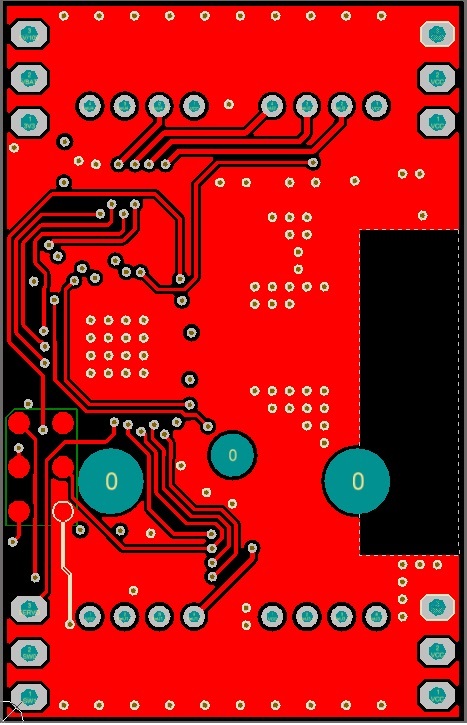

This is layer that has power suply lines. On this image it can be seen, that no track runs under RF section.