Hi,

We are using CC2640R2 controller. We have also initialized the TRF7970A as mentioned above. Also sending the inventory command after proper initialization.

Our tag supports ISO 15693 protocol. We have initialized registers accordingly.

//Sending Inventory command

TRF79x0_directCommand(TRF79X0_RESET_FIFO_CMD);//Reset Fifo

TRF79x0_directCommand(TRF79X0_TRANSMIT_CRC_CMD);//trans with CRC

TransBuff[ui8Offset++] = 0x3D;//

TransBuff[ui8Offset++] = (uint8_t)(Size>>8);

TransBuff[ui8Offset++] = (uint8_t)(Size<<4);

TransBuff[ui8Offset++] = 0x26;// Option flags

TransBuff[ui8Offset++] = 0x01;// Inventory Command

TransBuff[ui8Offset++] = 0x00;// Mask

//TransBuff[ui8Offset++] = 0x00;// wait time to process PICC Command

TRF79x0_writeCont(TransBuff,TRF79X0_TX_LENGTH_BYTE1_REG,ui8Offset);

Problem:

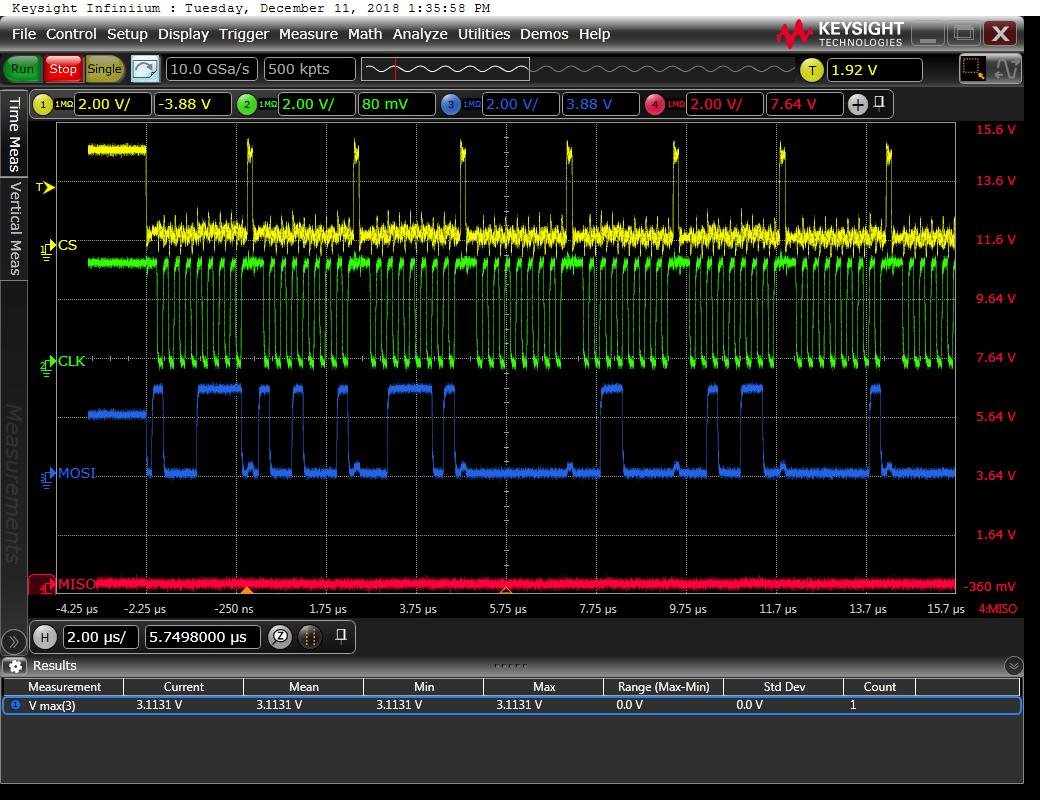

IRQ interrupt is not consistent. and fifo status register is always zero.

Can anybody support us from TI India on webex to share screen and see the problem?

Thank You,

Kuna