Other Parts Discussed in Thread: CC2590, CC2592

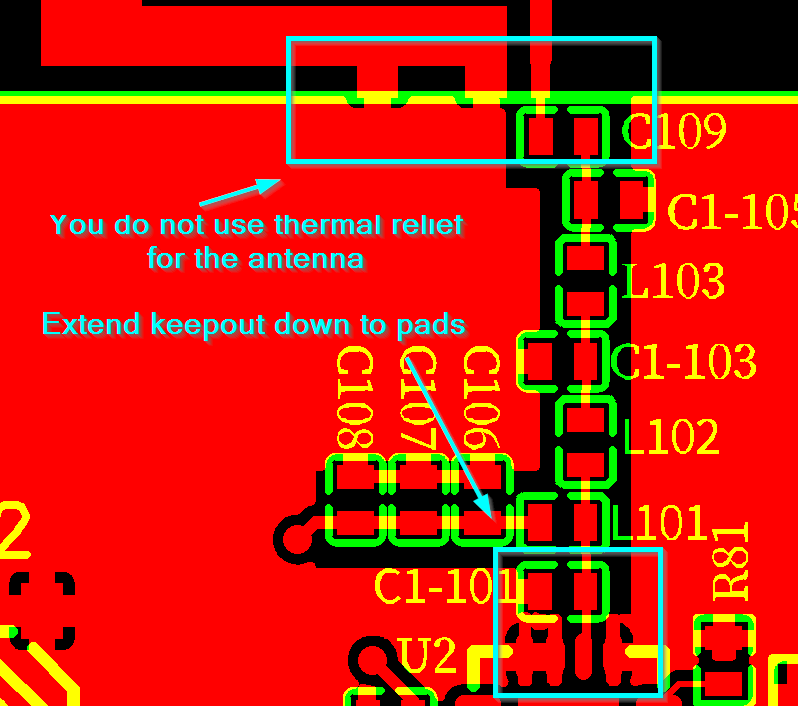

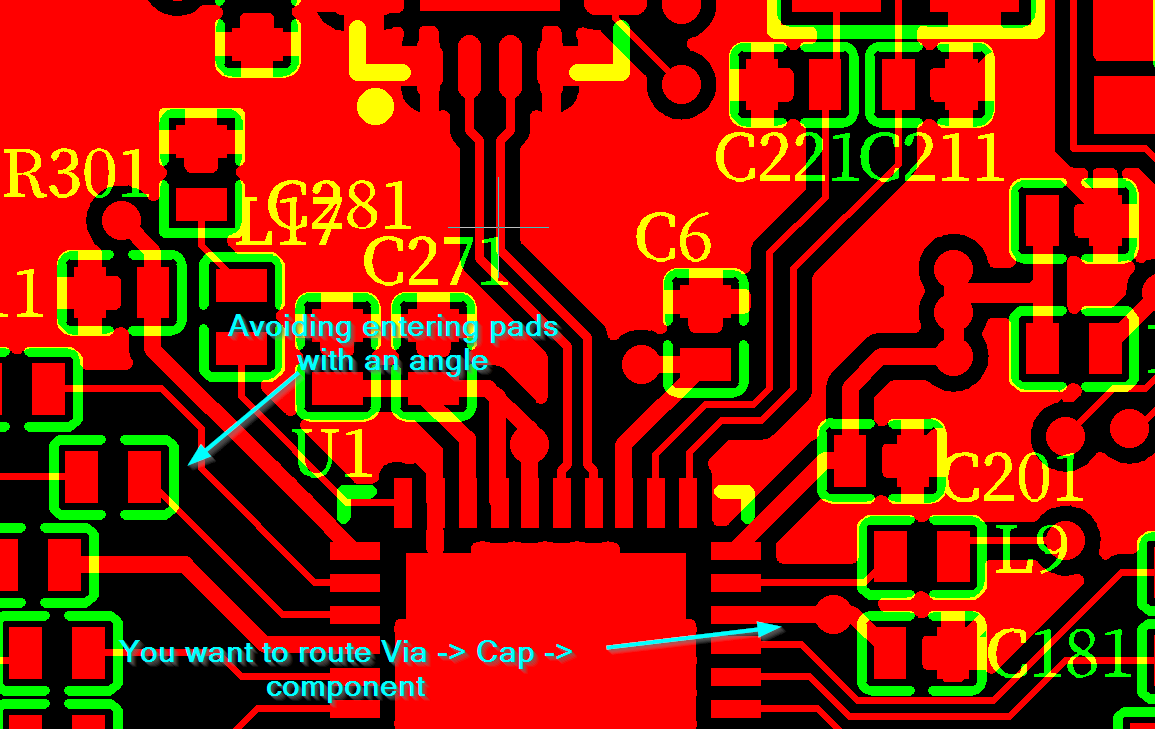

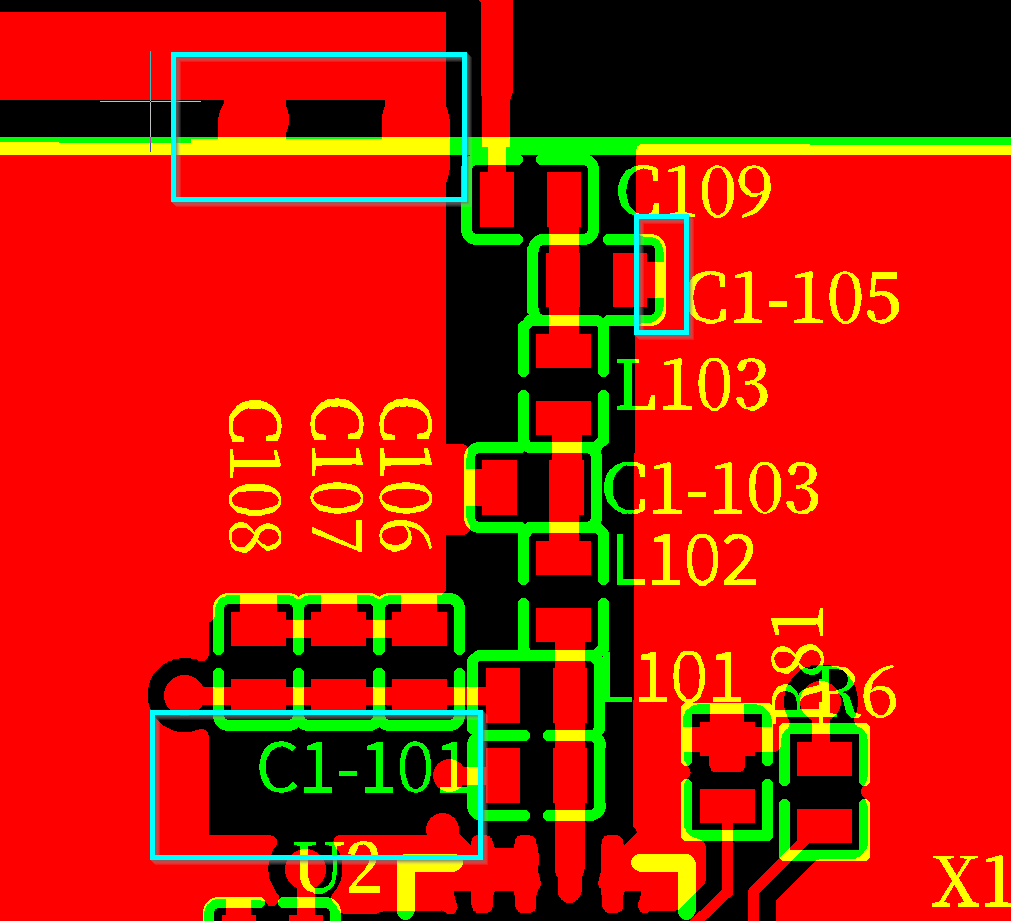

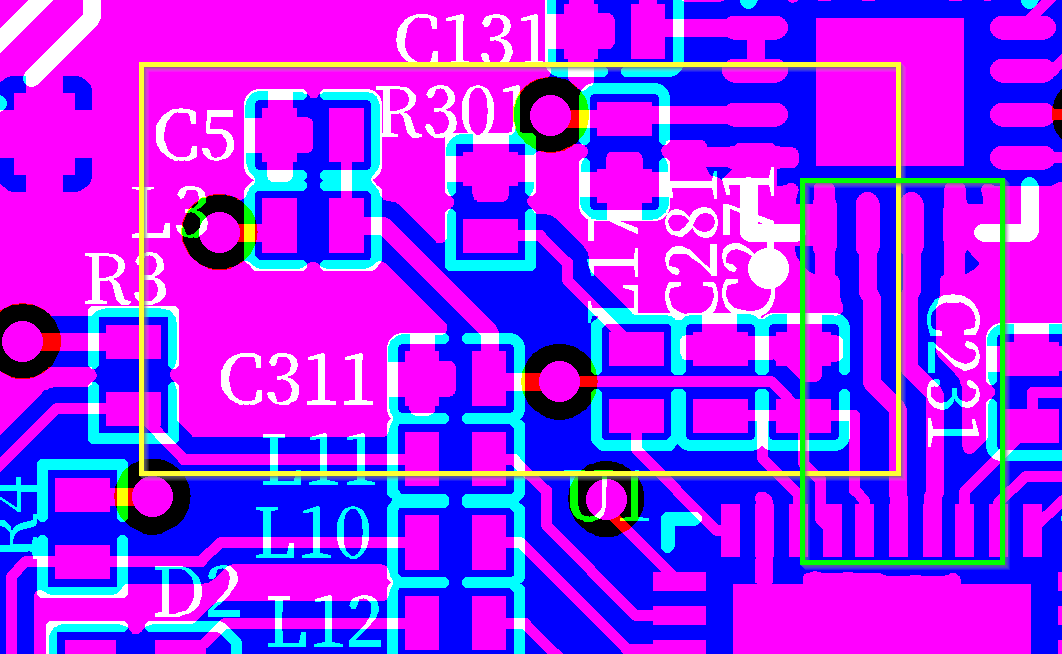

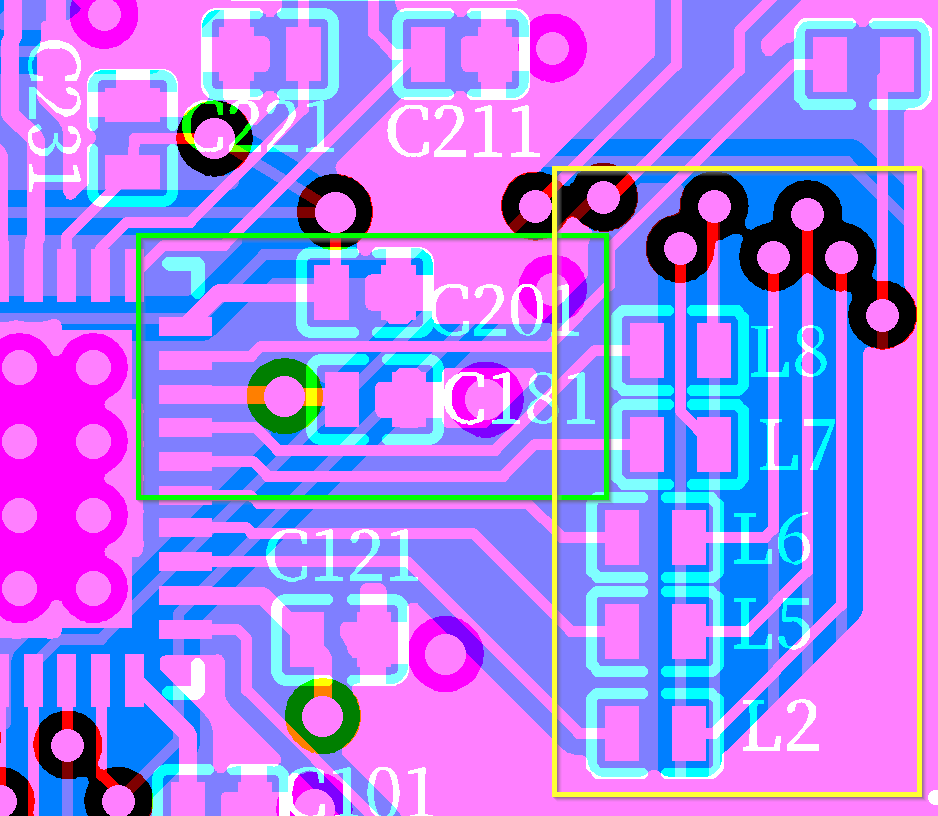

I have implemented the headset reference design for the PurePath CC8531. I made some changes to the power circuit eliminating the charger.

Unfortunately, I cant get it to work. It does not register via USB, nor can I connect to it using the CC Debugger. I understand that I have probably done something wrong, but after checking all the connections I am unable to figure it out. I have gone over all the traces and there are no breaks, also as far as I can tell all the power and ground connections are as they should. I'm really at a loss here

Any help would be greatly appreciated.

See below for the schematic: