Other Parts Discussed in Thread: SYSCONFIG

Hello.

I am working with an external flash memory chip that only supports SPI modes 0 and 3 (POL = 0, PHA = 0 OR POL = 1, PHA = 0).

When I configure the SPI driver to use modes 0 or 3 (SPI_POL0_PHA0 or SPI_POL1_PHA0), there is a pause between each 8-bit frame, where the CS line is briefly pulled high, ending any communications with the external chip. See image.

When I configure the SPI driver to modes 1 or 2 (SPI_POL1_PHA1 or SPI_POL0_PHA1). there is no frame pause, but the external chip doesn't support these modes. See image.

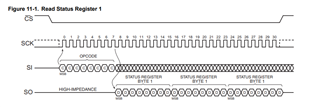

The exchange should look as follows from the flash chip datasheet. See image.

I found a suggestion to change .minDmaTransferSize in spiCC26X2DMAHWAttrs from default 10 to 1, but this didn't seem to have an impact.

Any help greatly appreciated!