Other Parts Discussed in Thread: MSP430FW423, MSP430FW425,

Hello,

1. We are producing working devices using MSP430FW423/MSP430FW425 and cc115l as radio transmitter.

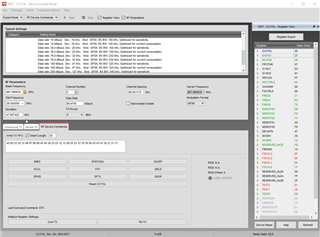

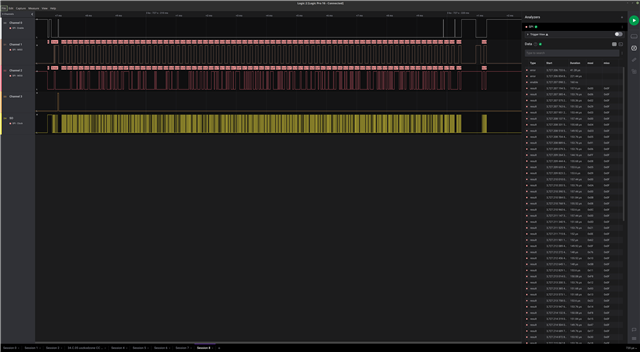

2. We are using configuration form RFStudio with default values for "100kb optimized for current consumption". Configuration process is shown on attachment1 and source for saleae logic2 is here: https://www.dropbox.com/s/whc609zdau98lty/34.C.05%20cc%20configuration%20attachement1.sal?dl=0

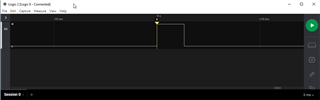

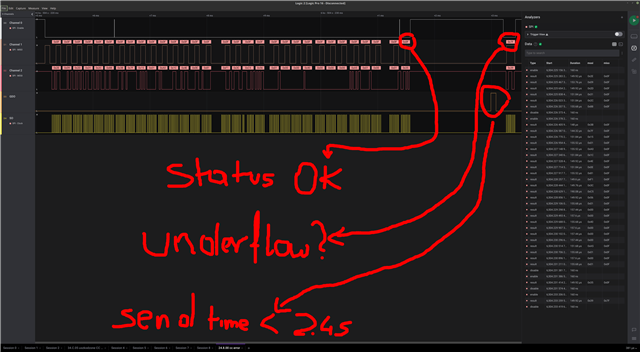

3. We are sending data and reacting on GDO pin that is setup for 0x06 (Asserts when sync word has been sent, and de-asserts at the end of the packet. The pin will de-assert if the TX FIFO underflows.) This is shown in attachement2 (https://www.dropbox.com/s/8cfund2a2snh4j3/34.C.05%20cc%20normal%20send%20attachement2.sal?dl=0)

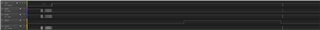

4. Now for our latest production we have problem with fifo underflow error randomly showing when trying to send frame. See attachement 3 (https://www.dropbox.com/s/784a0py70dfkn2u/34.C.05%20cc%20send%20with%20underflow%20attachement3.sal?dl=0)

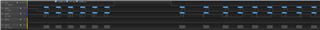

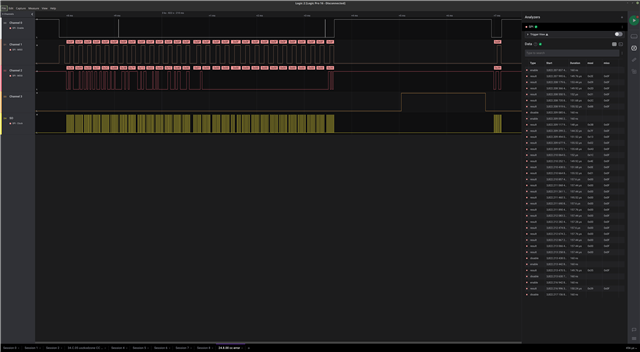

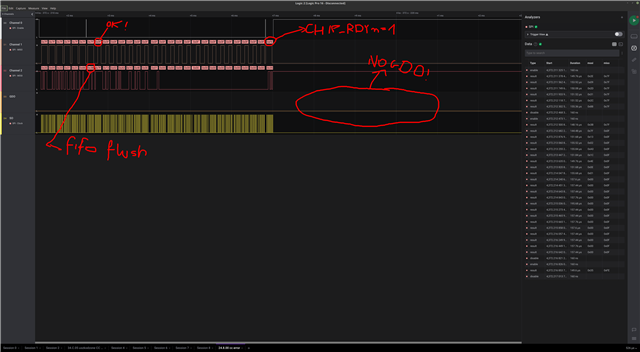

5. right after that frame we try to send next one. We perform fifo flush, which succeded and send data to fifo (status is 0x0F -> OK!!) and when performing STX command we get 0xFE status that indicates clock or voltage error. GDO is not asserted and module stays in TX mode. Carier is enabled and module consumes 35 mA of constant current. see attachement 4 (https://www.dropbox.com/s/vicgmbfnu87butl/34.C.05%20cc%20send%20CHIP_RDYn%201%20attachement4.sal?dl=0)

6. After that we have timeout in master uC and cc115l is reset and reprogrammed again. After reset it works as expected for couple of sends and randomly this problem returns. Sometimes after one minute, sometimes after hour. We Have about 8 errors during 4 hour period on current DUT. We haven't observed this issue on every device for now.

What could cause the problem?

Have you seen something similar on other projects?

What other data we could provide?

What we should test to know cause of this error?

I don't see relation to errata notes here but maye I'm missing something?

Regards

Maciej Łaski