Hi team,

Here's an issue from the customer may need your help:

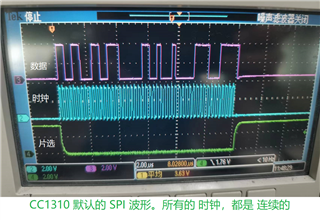

Call the SPI function library directly and modify the minDmaTransferSize to 1. If 5 bytes are written at a time, the oscilloscope shows 8*5 consecutive clock pulses with a CSN low (no interval, better SPI efficiency)

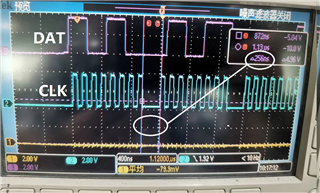

However, there is one device in the customer's actual circuit. When the device writes 5 bytes to it using SPI, it required to be separated by at least 2 every 8-tap clock before transmitting the next set of 8-tap clocks.

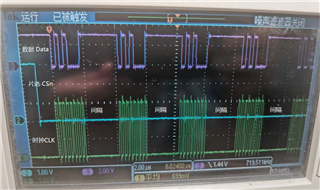

The customer would like to know how to increase this interval by modifying the SDK.

The oscilloscope waveform after implementation looks like the following picture:

Could you help check this case? Thanks.

Best Regards,

Cherry