Hi,

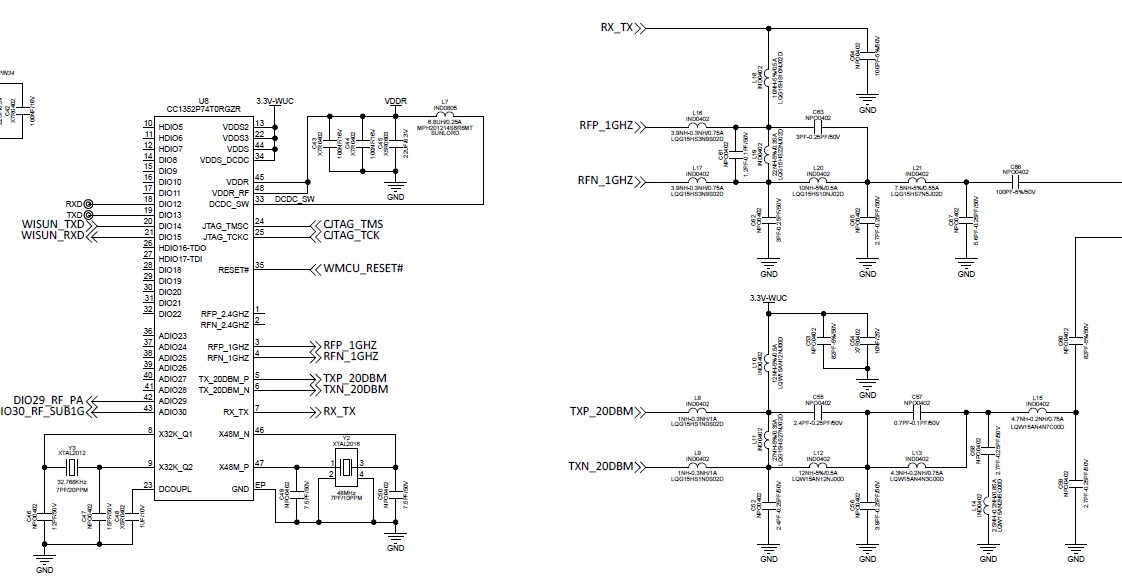

We are facing a consistent MCU reset issue on our own board when trying to join Wi-sun network with the 20dBm TX-only path. There is no issue joining with the 14dBm TX/RX path. Please refer to the below sch:

MCU: CC1352P74T0RGZR

2.4GHz path: unused

915MHz 14dBm path: component values follow CC1352PEM-XD7793-XD24-PA9093 reference design

915MHz 20dBm path: component values follow CC1352PEM-XD7793-XD24-PA9093 reference design

Every time the MCU tried to join our Wi-sun network with TX power between 14-20dBm (high power PA), the MCU will reset. This can be seen below:

Yellow: Pin 42, DIO29_RF_PA; Blue is a GPIO pin always outputting HIGH to indicate that the MCU is running.

Every time when the MCU tried to TX using the 20dBm path (DIO29_RF_PA to RF switch goes HIGH), the MCU went into a reset, indicated by a drop in GPIO voltage (blue). VDDS, VDDR and RST# voltage is stable when the reset occurs.

This is not happening on our board (14dBm path), or TI CC1352P7-1 development kit (both 14dBm and 20dBm path).

Interestingly, this reset issue is NOT happening on our board if we do a modulated/unmodulated TX, or packet TX&RX with SimpleRF Studio 7, on both 14dBm and 20dBm path.

We are using the below SDKs:

simplelink_cc13xx_cc26xx_sdk_5_40_00_40

simplelink_cc13xx_cc26xx_sdk_6_20_00_29

We have tried the following to no avail:

1. Turn off DCDC, remove L7 and use the global LDO.

2. Separate the 20dBm path supply from MCU supply. Power the 20dBm path (3.3V-WUC above L10) with a separate 3.3V supply.

3. Removed L16, L17 (in 14dBm path), removed C60, removed C57, L13.

Removing either L9 OR L10 will stop the reset issue. Removing L8 will not stop the issue.

Removing all other components in the 20dBm front end, leaving just L9, L10 & L11, the reset issue still persists.

We have ruled out the following:

1. Dip in DCDC VDDR

2. Dip in VDDS

3. Dip in RESET# signal

Any input is kindly appreciated.

Regards,

Yong