Other Parts Discussed in Thread: CC1312R, , SYSCONFIG

Hello,

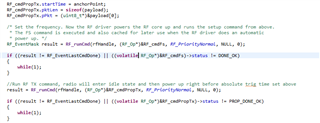

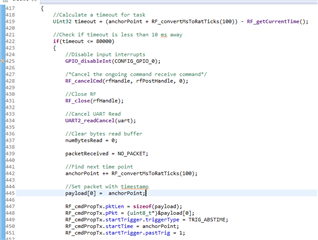

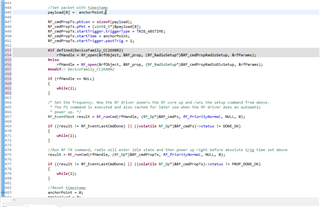

I am using the sub 1 GHz RF on the CC1352R1 to accomplish time synchronization between two CC1352R1 eval boards and to send timing signals. I am using TI-RTOS & SDK version 6.20.00.29. Once the clocks are synchronized, I calculate the next time a timing signal needs to be sent. I then use a clock object from the TI-RTOS clock module (explained here: TI-RTOS Kernel (SYS/BIOS) User's Guide, section 5.2), input the calculated time until the next time a signal needs to be sent as a timeout to the clock object. Then I use a period on the clock object to fire a callback function which outputs signals on an IO pin for the rest of the timing signals.

I take care of any latency delays due to the RF communication and processing overhead but I am seeing a jitter from the output of the clock module and GPIO pin of 5 - 10 microseconds.

Is there any way to get this jitter below a microsecond? Are there any changes or performance improvements I can make in the code or in TI-RTOS to reduce this jitter of the clock module and GPIO module? The signal I am comparing my output to is a hardwired signal that has a jitter of less than 25 nanoseconds, so any jitter on the order of microseconds is not due to the source signal.