Other Parts Discussed in Thread: CC1200, CC1312R, WMBUS, MSP430G2744

Hi experts,

My customer is using a CC1120 and it is not set in the RX FIFO even though it appears to be data received.

Could you please check if there is any setting error?

Regarding the register settings, They are referring to the SmartRF Studio values.

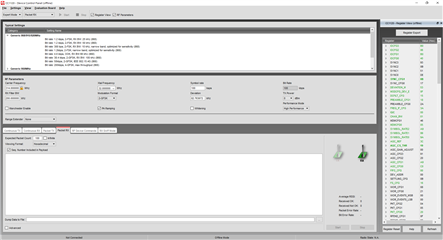

Attached is a screenshot of the configuration screen, an xml file, and an Excel file of the "register setting values".

[Environment]

[How to reproduce]

Set the register value in "Register setting value" and shift to Receive mode.

Calibration is performed manually.

Receive a 6-byte packet while polling the status register.

The status register changes as if a packet was received, but NUM_RXBYTES does not change from 0.

[Result]

Before packet reception

| Register | Value | Overview |

| MARCSTATE | 0x6D | MARC_STATE=RX |

| PQT_SYNC_ERR | 0x1F, 0x2F, 0x3F | |

| RX_STATUS (MODEM_STATUS1) |

0x11, 0x13 | RX FIFO EMPTY |

| LQI_VAL | 0x00 | |

| MARC_STATUS1 | 0x00 | |

| MARC_STATUS0 | 0x00 | |

| DEM_STATUS | 0x00 | |

| NUM_RXBYTES | 0x00 |

After packet reception

| Register | Value | Overview |

| MARCSTATE | 0x41 | MARC_STATE=IDLE |

| PQT_SYNC_ERR | 0x00 | |

| RX_STATUS (MODEM_STATUS1) |

0x91 | SYNC_FOUND, RX FIFO EMPTY |

| LQI_VAL | 0x81~0x84 | PKT_CRC_OK=CRC check ok |

| MARC_STATUS1 | 0x00 | |

| MARC_STATUS0 | 0x00 | |

| DEM_STATUS | 0x00 | |

| NUM_RXBYTES | 0x00 | (Received data is not set in the FIFO) |

Also, it would be helpful if you could share any check points or reference information to solve the problem.

Best regards,

O.H

<?xml version="1.0" encoding="ISO-8859-1"?>

<!DOCTYPE configuration SYSTEM "C:/Program Files (x86)/Texas Instruments/SmartRF Tools/SmartRF Studio 7/config/xml/configdata.dtd"[]>

<dcpanelconfiguration>

<Devicename>CC1120</Devicename>

<Description>Saved configuration data</Description>

<registersettings>

<Register>

<Name>AGC_CFG0</Name>

<Value>0xc0</Value>

</Register>

<Register>

<Name>AGC_CFG1</Name>

<Value>0xa9</Value>

</Register>

<Register>

<Name>AGC_CS_THR</Name>

<Value>0xef</Value>

</Register>

<Register>

<Name>AGC_REF</Name>

<Value>0x3c</Value>

</Register>

<Register>

<Name>CHAN_BW</Name>

<Value>0x01</Value>

</Register>

<Register>

<Name>DCFILT_CFG</Name>

<Value>0x15</Value>

</Register>

<Register>

<Name>DEVIATION_M</Name>

<Value>0x53</Value>

</Register>

<Register>

<Name>FIFO_CFG</Name>

<Value>0x00</Value>

</Register>

<Register>

<Name>FREQ1</Name>

<Value>0xc0</Value>

</Register>

<Register>

<Name>FREQ2</Name>

<Value>0x75</Value>

</Register>

<Register>

<Name>FREQ_IF_CFG</Name>

<Value>0x3a</Value>

</Register>

<Register>

<Name>FS_CAL0</Name>

<Value>0x0e</Value>

</Register>

<Register>

<Name>FS_CAL1</Name>

<Value>0x40</Value>

</Register>

<Register>

<Name>FS_CFG</Name>

<Value>0x16</Value>

</Register>

<Register>

<Name>FS_DIG0</Name>

<Value>0x5f</Value>

</Register>

<Register>

<Name>FS_DIG1</Name>

<Value>0x00</Value>

</Register>

<Register>

<Name>FS_DIVTWO</Name>

<Value>0x03</Value>

</Register>

<Register>

<Name>FS_DSM0</Name>

<Value>0x33</Value>

</Register>

<Register>

<Name>FS_DVC0</Name>

<Value>0x17</Value>

</Register>

<Register>

<Name>FS_PFD</Name>

<Value>0x50</Value>

</Register>

<Register>

<Name>FS_PRE</Name>

<Value>0x6e</Value>

</Register>

<Register>

<Name>FS_REG_DIV_CML</Name>

<Value>0x14</Value>

</Register>

<Register>

<Name>FS_SPARE</Name>

<Value>0xac</Value>

</Register>

<Register>

<Name>FS_VCO0</Name>

<Value>0xb4</Value>

</Register>

<Register>

<Name>IF_MIX_CFG</Name>

<Value>0x00</Value>

</Register>

<Register>

<Name>IOCFG0</Name>

<Value>0x40</Value>

</Register>

<Register>

<Name>IOCFG1</Name>

<Value>0xb0</Value>

</Register>

<Register>

<Name>IOCFG2</Name>

<Value>0x06</Value>

</Register>

<Register>

<Name>IOCFG3</Name>

<Value>0xb0</Value>

</Register>

<Register>

<Name>IQIC</Name>

<Value>0x00</Value>

</Register>

<Register>

<Name>MDMCFG0</Name>

<Value>0x05</Value>

</Register>

<Register>

<Name>MODCFG_DEV_E</Name>

<Value>0x0f</Value>

</Register>

<Register>

<Name>PA_CFG0</Name>

<Value>0x7a</Value>

</Register>

<Register>

<Name>PA_CFG2</Name>

<Value>0x5d</Value>

</Register>

<Register>

<Name>PKT_CFG0</Name>

<Value>0x20</Value>

</Register>

<Register>

<Name>PKT_LEN</Name>

<Value>0xff</Value>

</Register>

<Register>

<Name>PREAMBLE_CFG1</Name>

<Value>0x18</Value>

</Register>

<Register>

<Name>SYMBOL_RATE0</Name>

<Value>0x9a</Value>

</Register>

<Register>

<Name>SYMBOL_RATE1</Name>

<Value>0x99</Value>

</Register>

<Register>

<Name>SYMBOL_RATE2</Name>

<Value>0xa9</Value>

</Register>

<Register>

<Name>SYNC_CFG1</Name>

<Value>0x08</Value>

</Register>

<Register>

<Name>TOC_CFG</Name>

<Value>0x0a</Value>

</Register>

<Register>

<Name>XOSC1</Name>

<Value>0x03</Value>

</Register>

<Register>

<Name>XOSC5</Name>

<Value>0x0e</Value>

</Register>

</registersettings>

<dcpanel>

<Property name="m_chkRegView" role="44">2</Property>

<Property name="m_chkCmdView" role="44">0</Property>

<Property name="m_chkRfParameters" role="44">2</Property>

<Property name="m_cmbUserMode" role="46">1</Property>

<Property name="m_easyModeSettings" role="33">-1</Property>

<Property name="m_typicalSettings" role="33">-1</Property>

<Property name="m_testFuncPanel" role="37">2</Property>

</dcpanel>

<rfparameters>

<Property name="m_cmbFrontends" role="46">0</Property>

<Property name="m_chkHGMorBYP" role="44">2</Property>

<Property name="m_cmbEmRevs" role="46">-1</Property>

<Property name="Xtal Frequency" role="46">32.000000</Property>

</rfparameters>

<conttx>

<Property name="m_rbtModulated" role="45">1</Property>

<Property name="m_rbtUnmodulated" role="45">0</Property>

<Property name="m_cmbDataFormat" role="46">-1</Property>

<Property name="m_chkFreqSweep" role="44">0</Property>

<Property name="m_chkChanSweep" role="44">0</Property>

</conttx>

<contrx>

<Property name="m_cmbDataFormat" role="46">-1</Property>

<Property name="m_chkAutoScroll" role="44">2</Property>

</contrx>

<packettx>

<Property name="m_edtPayloadSize" role="42">30</Property>

<Property name="m_edtPacketCount" role="42">100</Property>

<Property name="m_edtPacketCountEsy" role="42">100</Property>

<Property name="m_edtRandomPacketData" role="42">13 0d 89 0a 1c db ae 32 20 9a 50 ee 40 78 36 fd 12 49 32 f6 9e 7d 49 dc ad 4f 14 f2 </Property>

<Property name="m_edtPacketData" role="42"></Property>

<Property name="m_edtAccessAddress" role="42"></Property>

<Property name="m_edtDeviceAddress" role="42"></Property>

<Property name="m_chkAddSeqNbr" role="44">2</Property>

<Property name="m_chkInfinite" role="44">0</Property>

<Property name="m_chkInfiniteEsy" role="44">0</Property>

<Property name="m_rbtRandom" role="45">1</Property>

<Property name="m_rbtText" role="45">0</Property>

<Property name="m_rbtHex" role="45">0</Property>

<Property name="m_chkAdvanced" role="44">0</Property>

</packettx>

<packetrx>

<Property name="m_edtPacketCount" role="42">100</Property>

<Property name="m_edtPacketCountEsy" role="42">100</Property>

<Property name="m_edtAccessAddress" role="42"></Property>

<Property name="m_chkInfinite" role="44">0</Property>

<Property name="m_chkInfiniteEsy" role="44">0</Property>

<Property name="m_cmbViewFormat" role="46">0</Property>

<Property name="m_chkSeqNbrIncluded" role="44">2</Property>

<Property name="m_edtDumpFile" role="42"></Property>

<Property name="m_chkAdvanced" role="44">0</Property>

<Property name="m_chk802154gMode" role="44">0</Property>

</packetrx>

<commandpanel>

<Property name="m_chkInsertLength" role="44">0</Property>

<Property name="m_edtTxFifo" role="42"></Property>

<Property name="m_edtRxFifo" role="42"></Property>

<Property name="m_cmbInstrInput" role="46">-1</Property>

</commandpanel>

<packetRxSniffMode>

<Property name="m_edtPreambleLength" role="42">24</Property>

<Property name="m_edtCarrierSenseThreshold" role="42">-90</Property>

<Property name="m_rbtRssi" role="45">1</Property>

<Property name="m_rbtPreamble" role="45">0</Property>

</packetRxSniffMode>

</dcpanelconfiguration>