Hi,

using CC112x for years now in FSK, I wonder why we don't use them outside FSK - we manufacture some thousand (legacy) OOK systems at 868Mhz per year; typical application are keyfob systems.

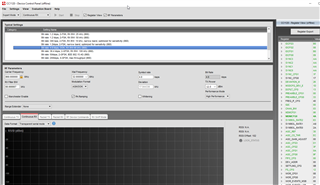

We can't change the protocols of these systems due to backward compatibility; a typical protocol timing is attached!

Today we use good-old TDA receiver chips and I asked my engineers, why they don't use our main RF chip CC11xx.

Reply was 'because you can't use them in ASK transprarent mode':

1. first they obviously can't deal with the long pause in between packet repetitions (we had the same issue with FSK, where at least we tuned the AFC as long as it fits. This doesn't work in ASK, as they told me).

2. then if they tried to use it with much shorter pauses, the sensivity was 20dB worse than with the TDAs

Can you advise if this is correct / how we could use CC's in that field?

thx