Hello, I have an application where we are seeing a lot of additional noise in the DCDC path of the 1350 chip. It causes up to a doubling of the standby current of the device, which is a severe hit on our battery life. We are currently failing the devices with this issue during production testing, so it would be great with some pointers to how we can solve this.

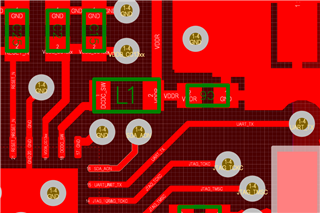

I am suspecting an issue with the inductor layout or the inductor selection. In this design we're using Taiyo Yuden CBMF1608T100K, which is an unshielded wirewound inductor, with this layout:

I have very limited experience with the DCDC design, so I'm looking for some pointers. I had a look at the design guideline https://www.ti.com/lit/an/swra640g/swra640g.pdf but didn't find the DCDC regulator part very helpful. The C6 capacitor power route is a bit unfortunate, if that could cause this issue?

Other notes:

- The issue affects about 2% of our tested devices.

- Issue seems to be specific to the CC1350-device: Swapping 1350 on a failed PCBA to a passed PCBA will still fail the same CC1350 component, and conversely the other CC1350 will still pass.

- Placing a piece of metal (I used an insulated screwdriver tip) between the DCDC inductor and the CC1350 chip will remove the noise, and reduce the standby current down to the acceptable level.

- Swapping the inductor to a shielded multilayer variant reduces the noise (and standby current) considerably. I tried Murata LQM18DN100M70L for example

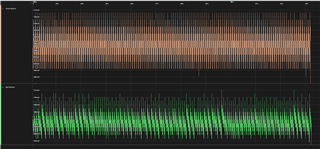

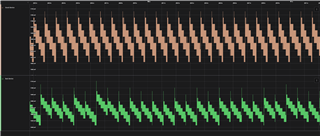

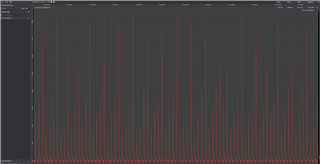

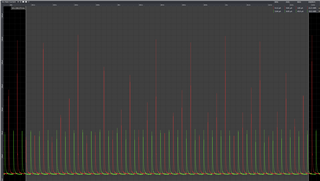

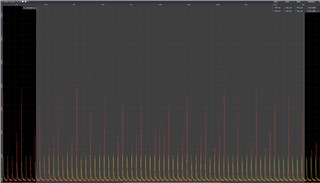

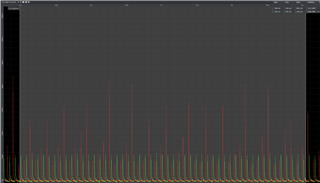

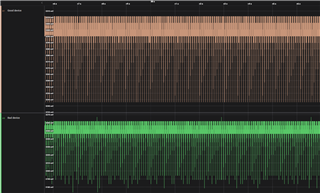

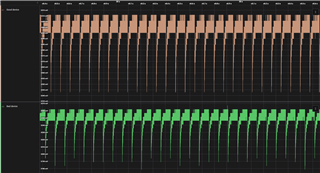

I captured the voltage on VDDR on both devices (powered from the same battery pack), and the "bad device" looks a lot more noisy. Again, I'm not sure what I'm looking for, so I'll be happy to capture more data if needed.

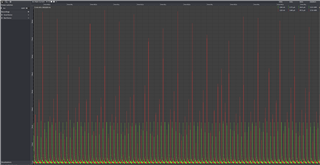

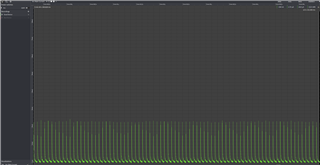

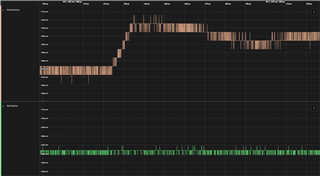

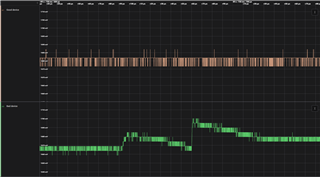

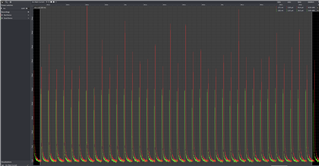

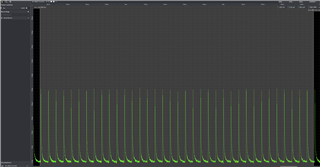

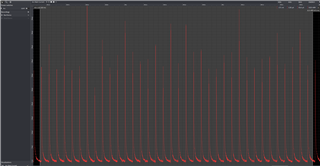

The issue is a lot more apparent in the current draw, so I'll attach some plots of that too: ("good" device in green / "bad" device in red)

Any pointers are greatly appreciated, thanks!