Other Parts Discussed in Thread: CC1101, , TEST2

Tool/software:

Hello,

I have a question regarding the project I am working on.

I have two boards that need to communicate with each other. One of them uses a CC1101 and the other one uses a CC1310.

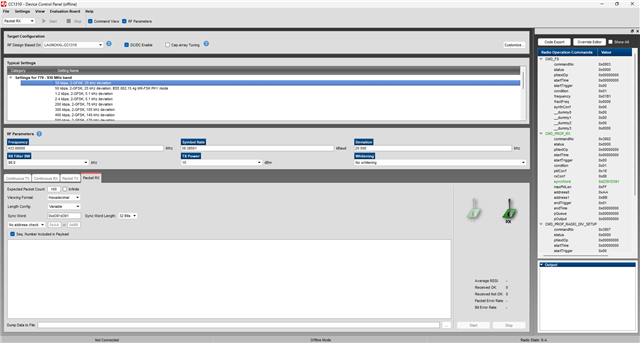

When the CC1101 is configured with Configuration 1 and the CC1310 is set as shown in Screenshot 1, the communication works.

When I export Screenshot 1 to code, it generates a file similar to the attached smartrf_settings1.txt.

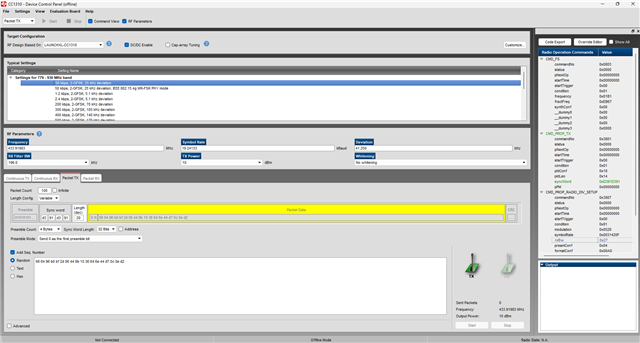

However, I would like to use Configuration 2 on the CC1101 side. For this, I configured the CC1310 as shown in Screenshot 2 and generated smartrf_settings2.txt. But in this case, communication does not work.

Could you please help me with this?

How should I configure the CC1310 to make it compatible with Configuration 2?

Configuration 1:

TI_write_reg(CCxxx0_IOCFG2,0x29); //GDO2 Output Pin Configuration

TI_write_reg(CCxxx0_IOCFG1,0x2E); //GDO1 Output Pin Configuration

TI_write_reg(CCxxx0_IOCFG0,0x06); //GDO0 Output Pin Configuration

TI_write_reg(CCxxx0_FIFOTHR,0x47); //RX FIFO and TX FIFO Thresholds

TI_write_reg(CCxxx0_SYNC1,0xD3); //Sync Word, High Byte

TI_write_reg(CCxxx0_SYNC0,0x91); //Sync Word, Low Byte

TI_write_reg(CCxxx0_PKTLEN,0xFF); //Packet Length

TI_write_reg(CCxxx0_PKTCTRL1,0x04);//Packet Automation Control

TI_write_reg(CCxxx0_PKTCTRL0,0x05);//Packet Automation Control

TI_write_reg(CCxxx0_ADDR,0x00); //Device Address

TI_write_reg(CCxxx0_CHANNR,0x00); //Channel Number

TI_write_reg(CCxxx0_FSCTRL1,0x06); //Frequency Synthesizer Control

TI_write_reg(CCxxx0_FSCTRL0,0x00); //Frequency Synthesizer Control

TI_write_reg(CCxxx0_FREQ2,0x10); //Frequency Control Word, High Byte

TI_write_reg(CCxxx0_FREQ1,0xA7); //Frequency Control Word, Middle Byte

TI_write_reg(CCxxx0_FREQ0,0x62); //Frequency Control Word, Low Byte

TI_write_reg(CCxxx0_MDMCFG4,0xCA); //Modem Configuration

TI_write_reg(CCxxx0_MDMCFG3,0x83); //Modem Configuration

TI_write_reg(CCxxx0_MDMCFG2,0x13); //Modem Configuration

TI_write_reg(CCxxx0_MDMCFG1,0x22); //Modem Configuration

TI_write_reg(CCxxx0_MDMCFG0,0xF8); //Modem Configuration

TI_write_reg(CCxxx0_DEVIATN,0x35); //Modem Deviation Setting

TI_write_reg(CCxxx0_MCSM2,0x07); //Main Radio Control State Machine Configuration

TI_write_reg(CCxxx0_MCSM1,0x30); //Main Radio Control State Machine Configuration

TI_write_reg(CCxxx0_MCSM0,0x18); //Main Radio Control State Machine Configuration

TI_write_reg(CCxxx0_FOCCFG,0x16); //Frequency Offset Compensation Configuration

TI_write_reg(CCxxx0_BSCFG,0x6C); //Bit Synchronization Configuration

TI_write_reg(CCxxx0_AGCCTRL2,0x03);//AGC Control

TI_write_reg(CCxxx0_AGCCTRL1,0x40);//AGC Control

TI_write_reg(CCxxx0_AGCCTRL0,0x91);//AGC Control

TI_write_reg(CCxxx0_WOREVT1,0x87); //High Byte Event0 Timeout

TI_write_reg(CCxxx0_WOREVT0,0x6B); //Low Byte Event0 Timeout

TI_write_reg(CCxxx0_WORCTRL,0xFB); //Wake On Radio Control

TI_write_reg(CCxxx0_FREND1,0x56); //Front End RX Configuration

TI_write_reg(CCxxx0_FREND0,0x10); //Front End TX Configuration

TI_write_reg(CCxxx0_FSCAL3,0xE9); //Frequency Synthesizer Calibration

TI_write_reg(CCxxx0_FSCAL2,0x2A); //Frequency Synthesizer Calibration

TI_write_reg(CCxxx0_FSCAL1,0x00); //Frequency Synthesizer Calibration

TI_write_reg(CCxxx0_FSCAL0,0x1F); //Frequency Synthesizer Calibration

TI_write_reg(CCxxx0_RCCTRL1,0x41); //RC Oscillator Configuration

TI_write_reg(CCxxx0_RCCTRL0,0x00); //RC Oscillator Configuration

TI_write_reg(CCxxx0_FSTEST,0x59); //Frequency Synthesizer Calibration Control

TI_write_reg(CCxxx0_PTEST,0x7F); //Production Test

TI_write_reg(CCxxx0_AGCTEST,0x3F); //AGC Test

TI_write_reg(CCxxx0_TEST2,0x81); //Various Test Settings

TI_write_reg(CCxxx0_TEST1,0x35); //Various Test Settings

TI_write_reg(CCxxx0_TEST0,0x09); //Various Test Settings

Configuration 2:

TI_write_reg(CCxxx0_IOCFG2,0x29); //GDO2 Output Pin Configuration

TI_write_reg(CCxxx0_IOCFG1,0x2E); //GDO1 Output Pin Configuration

TI_write_reg(CCxxx0_IOCFG0,0x06); //GDO0 Output Pin Configuration

TI_write_reg(CCxxx0_FIFOTHR,0x47); //RX FIFO and TX FIFO Thresholds

TI_write_reg(CCxxx0_SYNC1,0xD3); //Sync Word, High Byte

TI_write_reg(CCxxx0_SYNC0,0x91); //Sync Word, Low Byte

TI_write_reg(CCxxx0_PKTLEN,0x05); //Packet Length

TI_write_reg(CCxxx0_PKTCTRL1,0x04);//Packet Automation Control

TI_write_reg(CCxxx0_PKTCTRL0,0x01);//Packet Automation Control

TI_write_reg(CCxxx0_ADDR,0x00); //Device Address

TI_write_reg(CCxxx0_CHANNR,0x00); //Channel Number

TI_write_reg(CCxxx0_FSCTRL1,0x06); //Frequency Synthesizer Control

TI_write_reg(CCxxx0_FSCTRL0,0x00); //Frequency Synthesizer Control

TI_write_reg(CCxxx0_FREQ2,0x10); //Frequency Control Word, High Byte

TI_write_reg(CCxxx0_FREQ1,0xB0); //Frequency Control Word, Middle Byte

TI_write_reg(CCxxx0_FREQ0,0x71); //Frequency Control Word, Low Byte

TI_write_reg(CCxxx0_MDMCFG4,0x89); //Modem Configuration

TI_write_reg(CCxxx0_MDMCFG3,0x84); //Modem Configuration

TI_write_reg(CCxxx0_MDMCFG2,0x0E); //Modem Configuration

TI_write_reg(CCxxx0_MDMCFG1,0x22); //Modem Configuration

TI_write_reg(CCxxx0_MDMCFG0,0xF8); //Modem Configuration

TI_write_reg(CCxxx0_DEVIATN,0x45); //Modem Deviation Setting

TI_write_reg(CCxxx0_MCSM2,0x07); //Main Radio Control State Machine Configuration

TI_write_reg(CCxxx0_MCSM1,0x30); //Main Radio Control State Machine Configuration

TI_write_reg(CCxxx0_MCSM0,0x18); //Main Radio Control State Machine Configuration

TI_write_reg(CCxxx0_FOCCFG,0x76); //Frequency Offset Compensation Configuration

TI_write_reg(CCxxx0_BSCFG,0x6D); //Bit Synchronization Configuration

TI_write_reg(CCxxx0_AGCCTRL2,0xC7);//AGC Control

TI_write_reg(CCxxx0_AGCCTRL1,0x40);//AGC Control

TI_write_reg(CCxxx0_AGCCTRL0,0x91);//AGC Control

TI_write_reg(CCxxx0_WOREVT1,0x87); //High Byte Event0 Timeout

TI_write_reg(CCxxx0_WOREVT0,0x6B); //Low Byte Event0 Timeout

TI_write_reg(CCxxx0_WORCTRL,0xFB); //Wake On Radio Control

TI_write_reg(CCxxx0_FREND1,0xB6); //Front End RX Configuration

TI_write_reg(CCxxx0_FREND0,0x10); //Front End TX Configuration

TI_write_reg(CCxxx0_FSCAL3,0xE9); //Frequency Synthesizer Calibration

TI_write_reg(CCxxx0_FSCAL2,0x2A); //Frequency Synthesizer Calibration

TI_write_reg(CCxxx0_FSCAL1,0x00); //Frequency Synthesizer Calibration

TI_write_reg(CCxxx0_FSCAL0,0x1F); //Frequency Synthesizer Calibration

TI_write_reg(CCxxx0_RCCTRL1,0x41); //RC Oscillator Configuration

TI_write_reg(CCxxx0_RCCTRL0,0x00); //RC Oscillator Configuration

TI_write_reg(CCxxx0_FSTEST,0x59); //Frequency Synthesizer Calibration Control

TI_write_reg(CCxxx0_PTEST,0x7F); //Production Test

TI_write_reg(CCxxx0_AGCTEST,0x3F); //AGC Test

TI_write_reg(CCxxx0_TEST2,0x81); //Various Test Settings

TI_write_reg(CCxxx0_TEST1,0x35); //Various Test Settings

TI_write_reg(CCxxx0_TEST0,0x09); //Various Test Settings

Screenshot1:

//*********************************************************************************

// Generated by SmartRF Studio version 2.32.0 (build#409)

// The applied template is compatible with CC13x0 SDK version 2.10.xx.xx or newer.

// Device: CC1310 Rev. B (2.1).

//

//*********************************************************************************

//*********************************************************************************

// Parameter summary

// RX Address0: 0xAA

// RX Address1: 0xBB

// RX Address Mode: No address check

// Frequency: 433.00000 MHz

// Data Format: Serial mode disable

// Deviation: 20.500 kHz

// Packet Length Config: Variable

// Max Packet Length: 255

// Packet Length: 20

// Packet Data: 255

// RX Filter BW: 98.0 kHz

// Symbol Rate: 38.38501 kBaud

// Sync Word Length: 32 Bits

// TX Power: 15 dBm (requires define CCFG_FORCE_VDDR_HH = 1 in ccfg.c, see CC13xx/CC26xx Technical Reference Manual)

// Whitening: No whitening

//murat deneme

#include "smartrf_settings.h"

#include DeviceFamily_constructPath(rf_patches/rf_patch_cpe_genfsk.h)

#include DeviceFamily_constructPath(rf_patches/rf_patch_rfe_genfsk.h)

// TI-RTOS RF Mode Object

RF_Mode RF_prop =

{

.rfMode = RF_MODE_PROPRIETARY_SUB_1,

.cpePatchFxn = &rf_patch_cpe_genfsk,

.mcePatchFxn = 0,

.rfePatchFxn = &rf_patch_rfe_genfsk

};

// Overrides for CMD_PROP_RADIO_DIV_SETUP

uint32_t pOverrides[] =

{

// override_use_patch_prop_genfsk.xml

// PHY: Use MCE ROM bank 4, RFE RAM patch

MCE_RFE_OVERRIDE(0,4,0,1,0,0),

// override_synth_prop_863_930_div5.xml

// Synth: Set recommended RTRIM to 7

HW_REG_OVERRIDE(0x4038,0x0037),

// Synth: Set Fref to 4 MHz

(uint32_t)0x000684A3,

// Synth: Configure fine calibration setting

HW_REG_OVERRIDE(0x4020,0x7F00),

// Synth: Configure fine calibration setting

HW_REG_OVERRIDE(0x4064,0x0040),

// Synth: Configure fine calibration setting

(uint32_t)0xB1070503,

// Synth: Configure fine calibration setting

(uint32_t)0x05330523,

// Synth: Set loop bandwidth after lock to 20 kHz

(uint32_t)0x0A480583,

// Synth: Set loop bandwidth after lock to 20 kHz

(uint32_t)0x7AB80603,

// Synth: Configure VCO LDO (in ADI1, set VCOLDOCFG=0x9F to use voltage input reference)

ADI_REG_OVERRIDE(1,4,0x9F),

// Synth: Configure synth LDO (in ADI1, set SLDOCTL0.COMP_CAP=1)

ADI_HALFREG_OVERRIDE(1,7,0x4,0x4),

// Synth: Use 24 MHz XOSC as synth clock, enable extra PLL filtering

(uint32_t)0x02010403,

// Synth: Configure extra PLL filtering

(uint32_t)0x00108463,

// Synth: Increase synth programming timeout (0x04B0 RAT ticks = 300 us)

(uint32_t)0x04B00243,

// override_phy_rx_aaf_bw_0xd.xml

// Rx: Set anti-aliasing filter bandwidth to 0xD (in ADI0, set IFAMPCTL3[7:4]=0xD)

ADI_HALFREG_OVERRIDE(0,61,0xF,0xD),

// override_phy_gfsk_rx.xml

// Rx: Set LNA bias current trim offset to 3

(uint32_t)0x00038883,

// Rx: Freeze RSSI on sync found event

HW_REG_OVERRIDE(0x6084,0x35F1),

// override_phy_gfsk_pa_ramp_agc_reflevel_0x1a.xml

// Tx: Configure PA ramping setting (0x41). Rx: Set AGC reference level to 0x1A.

HW_REG_OVERRIDE(0x6088,0x411A),

// Tx: Configure PA ramping setting

HW_REG_OVERRIDE(0x608C,0x8213),

// override_phy_rx_rssi_offset_5db.xml

// Rx: Set RSSI offset to adjust reported RSSI by +5 dB (default: 0), trimmed for external bias and differential configuration

(uint32_t)0x00FB88A3,

// TX power override

// Tx: Set PA trim to max (in ADI0, set PACTL0=0xF8)

ADI_REG_OVERRIDE(0,12,0xF8),

(uint32_t)0xFFFFFFFF

};

// CMD_PROP_RADIO_DIV_SETUP

// Proprietary Mode Radio Setup Command for All Frequency Bands

rfc_CMD_PROP_RADIO_DIV_SETUP_t RF_cmdPropRadioDivSetup =

{

.commandNo = 0x3807,

.status = 0x0000,

.pNextOp = 0, // INSERT APPLICABLE POINTER: (uint8_t*)&xxx

.startTime = 0x00000000,

.startTrigger.triggerType = 0x0,

.startTrigger.bEnaCmd = 0x0,

.startTrigger.triggerNo = 0x0,

.startTrigger.pastTrig = 0x0,

.condition.rule = 0x1,

.condition.nSkip = 0x0,

.modulation.modType = 0x1,

.modulation.deviation = 0x52,

.symbolRate.preScale = 0xF,

.symbolRate.rateWord = 0x6244,

.symbolRate.decimMode = 0x0,

.rxBw = 0x24,

.preamConf.nPreamBytes = 0x4,

.preamConf.preamMode = 0x0,

.formatConf.nSwBits = 0x20,

.formatConf.bBitReversal = 0x0,

.formatConf.bMsbFirst = 0x1,

.formatConf.fecMode = 0x0,

.formatConf.whitenMode = 0x0,

.config.frontEndMode = 0x0,

.config.biasMode = 0x1,

.config.analogCfgMode = 0x0,

.config.bNoFsPowerUp = 0x0,

.txPower = 0x913F,

.pRegOverride = pOverrides,

.centerFreq = 0x01B1,

.intFreq = 0x8000,

.loDivider = 0x0A

};

// CMD_FS

// Frequency Synthesizer Programming Command

rfc_CMD_FS_t RF_cmdFs =

{

.commandNo = 0x0803,

.status = 0x0000,

.pNextOp = 0, // INSERT APPLICABLE POINTER: (uint8_t*)&xxx

.startTime = 0x00000000,

.startTrigger.triggerType = 0x0,

.startTrigger.bEnaCmd = 0x0,

.startTrigger.triggerNo = 0x0,

.startTrigger.pastTrig = 0x0,

.condition.rule = 0x1,

.condition.nSkip = 0x0,

.frequency = 0x01B1,

.fractFreq = 0x0000,

.synthConf.bTxMode = 0x0,

.synthConf.refFreq = 0x0,

.__dummy0 = 0x00,

.__dummy1 = 0x00,

.__dummy2 = 0x00,

.__dummy3 = 0x0000

};

// CMD_PROP_RX

// Proprietary Mode Receive Command

rfc_CMD_PROP_RX_t RF_cmdPropRx =

{

.commandNo = 0x3802,

.status = 0x0000,

.pNextOp = 0, // INSERT APPLICABLE POINTER: (uint8_t*)&xxx

.startTime = 0x00000000,

.startTrigger.triggerType = 0x0,

.startTrigger.bEnaCmd = 0x0,

.startTrigger.triggerNo = 0x0,

.startTrigger.pastTrig = 0x0,

.condition.rule = 0x1,

.condition.nSkip = 0x0,

.pktConf.bFsOff = 0x0,

.pktConf.bRepeatOk = 0x0,

.pktConf.bRepeatNok = 0x0,

.pktConf.bUseCrc = 0x1,

.pktConf.bVarLen = 0x1,

.pktConf.bChkAddress = 0x0,

.pktConf.endType = 0x0,

.pktConf.filterOp = 0x0,

.rxConf.bAutoFlushIgnored = 0x0,

.rxConf.bAutoFlushCrcErr = 0x0,

.rxConf.bIncludeHdr = 0x1,

.rxConf.bIncludeCrc = 0x0,

.rxConf.bAppendRssi = 0x0,

.rxConf.bAppendTimestamp = 0x0,

.rxConf.bAppendStatus = 0x1,

.syncWord = 0xD391D391,

.maxPktLen = 0xFF,

.address0 = 0xAA,

.address1 = 0xBB,

.endTrigger.triggerType = 0x1,

.endTrigger.bEnaCmd = 0x0,

.endTrigger.triggerNo = 0x0,

.endTrigger.pastTrig = 0x0,

.endTime = 0x00000000,

.pQueue = 0, // INSERT APPLICABLE POINTER: (dataQueue_t*)&xxx

.pOutput = 0 // INSERT APPLICABLE POINTER: (uint8_t*)&xxx

};

// CMD_PROP_TX

// Proprietary Mode Transmit Command

rfc_CMD_PROP_TX_t RF_cmdPropTx =

{

.commandNo = 0x3801,

.status = 0x0000,

.pNextOp = 0, // INSERT APPLICABLE POINTER: (uint8_t*)&xxx

.startTime = 0x00000000,

.startTrigger.triggerType = 0x0,

.startTrigger.bEnaCmd = 0x0,

.startTrigger.triggerNo = 0x0,

.startTrigger.pastTrig = 0x0,

.condition.rule = 0x1,

.condition.nSkip = 0x0,

.pktConf.bFsOff = 0x0,

.pktConf.bUseCrc = 0x1,

.pktConf.bVarLen = 0x1,

.pktLen = 0x14,

.syncWord = 0xD391D391,

.pPkt = 0 // INSERT APPLICABLE POINTER: (uint8_t*)&xxx

};

Screenshot2:

//*********************************************************************************

// Generated by SmartRF Studio version 2.32.0 (build#409)

// The applied template is compatible with CC13x0 SDK version 2.10.xx.xx or newer.

// Device: CC1310 Rev. B (2.1).

//

//*********************************************************************************

//*********************************************************************************

// Parameter summary

// RX Address0: 0x00

// RX Address1: 0x00

// RX Address Mode: No address check

// Frequency: 433.91983 MHz

// Data Format: Serial mode disable

// Deviation: 41.250 kHz

// Packet Length Config: Variable

// Max Packet Length: 255

// Packet Length: 20

// Packet Data: 255

// RX Filter BW: 196.0 kHz

// Symbol Rate: 19.24133 kBaud

// Sync Word Length: 32 Bits

// TX Power: 10 dBm

// Whitening: No whitening

#include "smartrf_settings.h"

#include DeviceFamily_constructPath(rf_patches/rf_patch_cpe_genfsk.h)

#include DeviceFamily_constructPath(rf_patches/rf_patch_rfe_genfsk.h)

// TI-RTOS RF Mode Object

RF_Mode RF_prop =

{

.rfMode = RF_MODE_PROPRIETARY_SUB_1,

.cpePatchFxn = &rf_patch_cpe_genfsk,

.mcePatchFxn = 0,

.rfePatchFxn = &rf_patch_rfe_genfsk

};

// Overrides for CMD_PROP_RADIO_DIV_SETUP

uint32_t pOverrides[] =

{

// override_use_patch_prop_genfsk.xml

// PHY: Use MCE ROM bank 4, RFE RAM patch

MCE_RFE_OVERRIDE(0,4,0,1,0,0),

// override_synth_prop_863_930_div5.xml

// Synth: Set recommended RTRIM to 7

HW_REG_OVERRIDE(0x4038,0x0037),

// Synth: Set Fref to 4 MHz

(uint32_t)0x000684A3,

// Synth: Configure fine calibration setting

HW_REG_OVERRIDE(0x4020,0x7F00),

// Synth: Configure fine calibration setting

HW_REG_OVERRIDE(0x4064,0x0040),

// Synth: Configure fine calibration setting

(uint32_t)0xB1070503,

// Synth: Configure fine calibration setting

(uint32_t)0x05330523,

// Synth: Set loop bandwidth after lock to 20 kHz

(uint32_t)0x0A480583,

// Synth: Set loop bandwidth after lock to 20 kHz

(uint32_t)0x7AB80603,

// Synth: Configure VCO LDO (in ADI1, set VCOLDOCFG=0x9F to use voltage input reference)

ADI_REG_OVERRIDE(1,4,0x9F),

// Synth: Configure synth LDO (in ADI1, set SLDOCTL0.COMP_CAP=1)

ADI_HALFREG_OVERRIDE(1,7,0x4,0x4),

// Synth: Use 24 MHz XOSC as synth clock, enable extra PLL filtering

(uint32_t)0x02010403,

// Synth: Configure extra PLL filtering

(uint32_t)0x00108463,

// Synth: Increase synth programming timeout (0x04B0 RAT ticks = 300 us)

(uint32_t)0x04B00243,

// override_phy_rx_aaf_bw_0xd.xml

// Rx: Set anti-aliasing filter bandwidth to 0xD (in ADI0, set IFAMPCTL3[7:4]=0xD)

ADI_HALFREG_OVERRIDE(0,61,0xF,0xD),

// override_phy_gfsk_rx.xml

// Rx: Set LNA bias current trim offset to 3

(uint32_t)0x00038883,

// Rx: Freeze RSSI on sync found event

HW_REG_OVERRIDE(0x6084,0x35F1),

// override_phy_gfsk_pa_ramp_agc_reflevel_0x1a.xml

// Tx: Configure PA ramping setting (0x41). Rx: Set AGC reference level to 0x1A.

HW_REG_OVERRIDE(0x6088,0x411A),

// Tx: Configure PA ramping setting

HW_REG_OVERRIDE(0x608C,0x8213),

// override_phy_rx_rssi_offset_5db.xml

// Rx: Set RSSI offset to adjust reported RSSI by +5 dB (default: 0), trimmed for external bias and differential configuration

(uint32_t)0x00FB88A3,

(uint32_t)0xFFFFFFFF

};

// CMD_PROP_RADIO_DIV_SETUP

// Proprietary Mode Radio Setup Command for All Frequency Bands

rfc_CMD_PROP_RADIO_DIV_SETUP_t RF_cmdPropRadioDivSetup =

{

.commandNo = 0x3807,

.status = 0x0000,

.pNextOp = 0, // INSERT APPLICABLE POINTER: (uint8_t*)&xxx

.startTime = 0x00000000,

.startTrigger.triggerType = 0x0,

.startTrigger.bEnaCmd = 0x0,

.startTrigger.triggerNo = 0x0,

.startTrigger.pastTrig = 0x0,

.condition.rule = 0x0,

.condition.nSkip = 0x0,

.modulation.modType = 0x0,

.modulation.deviation = 0xA5,

.symbolRate.preScale = 0xF,

.symbolRate.rateWord = 0x3142,

.symbolRate.decimMode = 0x0,

.rxBw = 0x27,

.preamConf.nPreamBytes = 0x4,

.preamConf.preamMode = 0x0,

.formatConf.nSwBits = 0x20,

.formatConf.bBitReversal = 0x0,

.formatConf.bMsbFirst = 0x1,

.formatConf.fecMode = 0xA,

.formatConf.whitenMode = 0x0,

.config.frontEndMode = 0x0,

.config.biasMode = 0x1,

.config.analogCfgMode = 0x0,

.config.bNoFsPowerUp = 0x0,

.txPower = 0x46CB,

.pRegOverride = pOverrides,

.centerFreq = 0x01B1,

.intFreq = 0x8000,

.loDivider = 0x0A

};

// CMD_FS

// Frequency Synthesizer Programming Command

rfc_CMD_FS_t RF_cmdFs =

{

.commandNo = 0x0803,

.status = 0x0000,

.pNextOp = 0, // INSERT APPLICABLE POINTER: (uint8_t*)&xxx

.startTime = 0x00000000,

.startTrigger.triggerType = 0x0,

.startTrigger.bEnaCmd = 0x0,

.startTrigger.triggerNo = 0x0,

.startTrigger.pastTrig = 0x0,

.condition.rule = 0x1,

.condition.nSkip = 0x0,

.frequency = 0x01B1,

.fractFreq = 0xEB7A,

.synthConf.bTxMode = 0x0,

.synthConf.refFreq = 0x0,

.__dummy0 = 0x00,

.__dummy1 = 0x00,

.__dummy2 = 0x00,

.__dummy3 = 0x0000

};

// CMD_PROP_RX

// Proprietary Mode Receive Command

rfc_CMD_PROP_RX_t RF_cmdPropRx =

{

.commandNo = 0x3802,

.status = 0x0000,

.pNextOp = 0, // INSERT APPLICABLE POINTER: (uint8_t*)&xxx

.startTime = 0x00000000,

.startTrigger.triggerType = 0x0,

.startTrigger.bEnaCmd = 0x0,

.startTrigger.triggerNo = 0x0,

.startTrigger.pastTrig = 0x0,

.condition.rule = 0x1,

.condition.nSkip = 0x0,

.pktConf.bFsOff = 0x0,

.pktConf.bRepeatOk = 0x0,

.pktConf.bRepeatNok = 0x0,

.pktConf.bUseCrc = 0x1,

.pktConf.bVarLen = 0x1,

.pktConf.bChkAddress = 0x0,

.pktConf.endType = 0x0,

.pktConf.filterOp = 0x0,

.rxConf.bAutoFlushIgnored = 0x0,

.rxConf.bAutoFlushCrcErr = 0x0,

.rxConf.bIncludeHdr = 0x1,

.rxConf.bIncludeCrc = 0x0,

.rxConf.bAppendRssi = 0x0,

.rxConf.bAppendTimestamp = 0x0,

.rxConf.bAppendStatus = 0x1,

.syncWord = 0xD391D391,

.maxPktLen = 0xFF,

.address0 = 0x00,

.address1 = 0x00,

.endTrigger.triggerType = 0x1,

.endTrigger.bEnaCmd = 0x0,

.endTrigger.triggerNo = 0x0,

.endTrigger.pastTrig = 0x0,

.endTime = 0x00000000,

.pQueue = 0, // INSERT APPLICABLE POINTER: (dataQueue_t*)&xxx

.pOutput = 0 // INSERT APPLICABLE POINTER: (uint8_t*)&xxx

};

// CMD_PROP_TX

// Proprietary Mode Transmit Command

rfc_CMD_PROP_TX_t RF_cmdPropTx =

{

.commandNo = 0x3801,

.status = 0x0000,

.pNextOp = 0, // INSERT APPLICABLE POINTER: (uint8_t*)&xxx

.startTime = 0x00000000,

.startTrigger.triggerType = 0x0,

.startTrigger.bEnaCmd = 0x0,

.startTrigger.triggerNo = 0x0,

.startTrigger.pastTrig = 0x0,

.condition.rule = 0x1,

.condition.nSkip = 0x0,

.pktConf.bFsOff = 0x0,

.pktConf.bUseCrc = 0x1,

.pktConf.bVarLen = 0x1,

.pktLen = 0x14,

.syncWord = 0xD391D391,

.pPkt = 0 // INSERT APPLICABLE POINTER: (uint8_t*)&xxx

};