Hi,

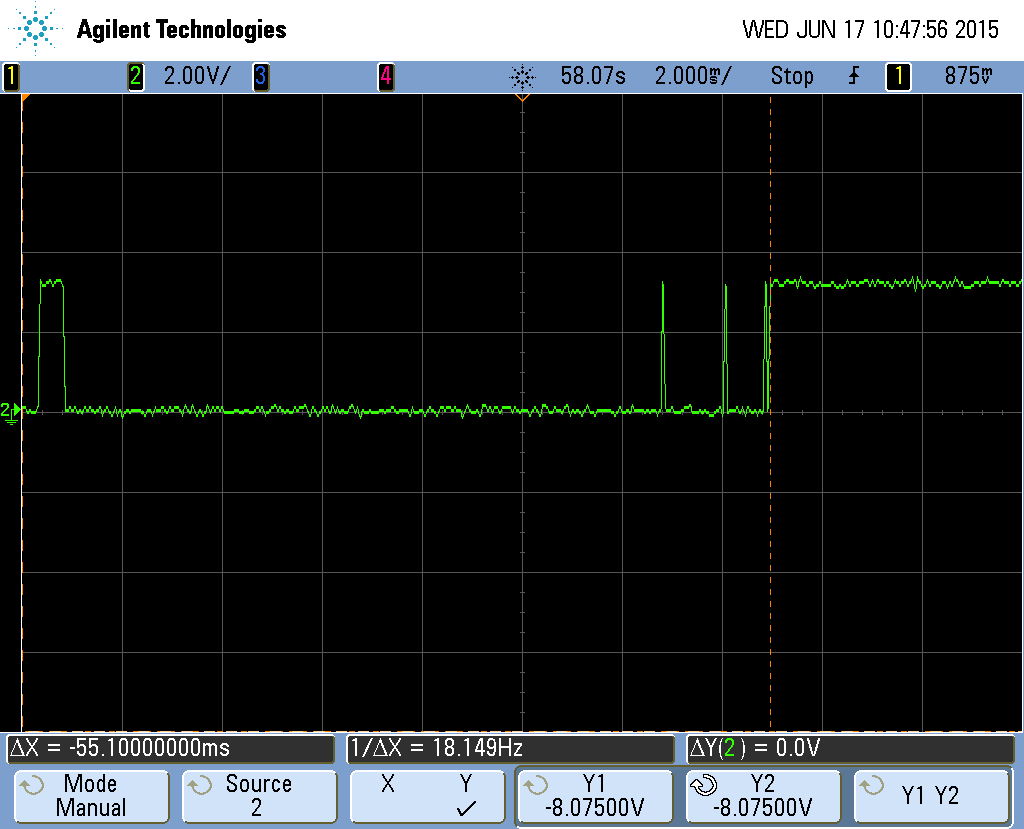

We are using CC112x Evaluation Module Kit on 433MHz. We send a question and listen to an answer. There is noise at the end of longer low level state in the answer (plots below). That noise is practically always in that place. We think that proper registers settings may remove (or degrade) the noise. Please see our reg settings and plots and help.

We work on 433,82MHz, 2-FSK, deviation 6,3kHz, 2,4kbaud, transparent mode. Settings were taken from RFStudio.

// Rf settings for CC1120

RF_SETTINGS code rfSettings = {

0xB0, // IOCFG3 GPIO3 IO Pin Configuration

0x08, // IOCFG2 GPIO2 IO Pin Configuration

0xB0, // IOCFG1 GPIO1 IO Pin Configuration

0x09, // IOCFG0 GPIO0 IO Pin Configuration

0xAA, // SYNC3 Sync Word Configuration [31:24]

0xAA, // SYNC2 Sync Word Configuration [23:16]

0xAA, // SYNC1 Sync Word Configuration [15:8]

0xAA, // SYNC0 Sync Word Configuration [7:0]

0x0B, // SYNC_CFG1 Sync Word Detection Configuration Reg. 1

0x03, // SYNC_CFG0 Sync Word Length Configuration Reg. 0

0x9D, // DEVIATION_M Frequency Deviation Configuration

0x1C, // DCFILT_CFG Digital DC Removal Configuration

0x00, // PREAMBLE_CFG1 Preamble Length Configuration Reg. 1

0x0A, // PREAMBLE_CFG0 Preamble Detection Configuration Reg. 0

0x46, // IQIC Digital Image Channel Compensation Configuration

0x04, // CHAN_BW Channel Filter Configuration

0x06, // MDMCFG1 General Modem Parameter Configuration Reg. 1

0x4A, // MDMCFG0 General Modem Parameter Configuration Reg. 0

0x53, // SYMBOL_RATE2 Symbol Rate Configuration Exponent and Mantissa [1..

0x20, // AGC_REF AGC Reference Level Configuration

0x19, // AGC_CS_THR Carrier Sense Threshold Configuration

0x0A, // AGC_CFG1 Automatic Gain Control Configuration Reg. 1

0xCF, // AGC_CFG0 Automatic Gain Control Configuration Reg. 0

0x00, // FIFO_CFG FIFO Configuration

0x14, // FS_CFG Frequency Synthesizer Configuration

0x07, // PKT_CFG2 Packet Configuration Reg. 2

0x00, // PKT_CFG1 Packet Configuration Reg. 1

0x20, // PKT_CFG0 Packet Configuration Reg. 0

0x74, // PA_CFG2 Power Amplifier Configuration Reg. 2

0x6E, // PA_CFG0 Power Amplifier Configuration Reg. 0

0xFF, // PKT_LEN Packet Length Configuration

0x00, // IF_MIX_CFG IF Mix Configuration

0x22, // FREQOFF_CFG Frequency Offset Correction Configuration

0x6C, // FREQ2 Frequency Configuration [23:16]

0x74, // FREQ1 Frequency Configuration [15:8]

0x7B, // FREQ0 Frequency Configuration [7:0]

0x00, // FS_DIG1 Frequency Synthesizer Digital Reg. 1

0x5F, // FS_DIG0 Frequency Synthesizer Digital Reg. 0

0x40, // FS_CAL1 Frequency Synthesizer Calibration Reg. 1

0x0E, // FS_CAL0 Frequency Synthesizer Calibration Reg. 0

0x03, // FS_DIVTWO Frequency Synthesizer Divide by 2

0x33, // FS_DSM0 FS Digital Synthesizer Module Configuration Reg. 0

0x17, // FS_DVC0 Frequency Synthesizer Divider Chain Configuration ..

0x50, // FS_PFD Frequency Synthesizer Phase Frequency Detector Con..

0x6E, // FS_PRE Frequency Synthesizer Prescaler Configuration

0x14, // FS_REG_DIV_CML Frequency Synthesizer Divider Regulator Configurat..

0xAC, // FS_SPARE Frequency Synthesizer Spare

0xB4, // FS_VCO0 FS Voltage Controlled Oscillator Configuration Reg..

0x0E, // XOSC5 Crystal Oscillator Configuration Reg. 5

0x03, // XOSC1 Crystal Oscillator Configuration Reg. 1

0x08, // SERIAL_STATUS Serial Status

};

Closer look:

Patrycjusz Bunko