Other Parts Discussed in Thread: TEST2

Hello!,

after a long time trying i decidet to post here my issue :).

What i have:

Smartrf with CC1101 for testing purposes

Logic analyzer - cheap one

Teensy with two CC1101 on SPI

Right now i am having issues with CC1101 setup. I was able to manage right parameters for my case (i async i am receiving right data):

halRfWriteReg(IOCFG2,0x0E); //GDO2 Output Pin Configuration

halRfWriteReg(IOCFG0,0x0D); //GDO0 Output Pin Configuration

halRfWriteReg(FIFOTHR,0x47); //RX FIFO and TX FIFO Thresholds

halRfWriteReg(SYNC1,0xAA); //Sync Word, High Byte

halRfWriteReg(SYNC0,0xB2); //Sync Word, Low Byte

halRfWriteReg(PKTLEN,0x3D); //Packet Length

halRfWriteReg(PKTCTRL0,0x32); //Packet Automation Control

halRfWriteReg(FSCTRL1,0x06); //Frequency Synthesizer Control

halRfWriteReg(FREQ2,0x10); //Frequency Control Word, High Byte

halRfWriteReg(FREQ1,0xB5); //Frequency Control Word, Middle Byte

halRfWriteReg(FREQ0,0x90); //Frequency Control Word, Low Byte

halRfWriteReg(MDMCFG4,0x87); //Modem Configuration

halRfWriteReg(MDMCFG3,0x12); //Modem Configuration

halRfWriteReg(MDMCFG2,0x38); //Modem Configuration

halRfWriteReg(DEVIATN,0x15); //Modem Deviation Setting

halRfWriteReg(MCSM0,0x18); //Main Radio Control State Machine Configuration

halRfWriteReg(FOCCFG,0x16); //Frequency Offset Compensation Configuration

halRfWriteReg(WORCTRL,0xFB); //Wake On Radio Control

halRfWriteReg(FREND0,0x17); //Front End TX Configuration

halRfWriteReg(FSCAL3,0xE9); //Frequency Synthesizer Calibration

halRfWriteReg(FSCAL2,0x2A); //Frequency Synthesizer Calibration

halRfWriteReg(FSCAL1,0x00); //Frequency Synthesizer Calibration

halRfWriteReg(FSCAL0,0x1F); //Frequency Synthesizer Calibration

halRfWriteReg(TEST2,0x81); //Various Test Settings

halRfWriteReg(TEST1,0x35); //Various Test Settings

halRfWriteReg(TEST0,0x09); //Various Test Settings

halRfWriteReg(VERSION,0x14); //Chip ID

halRfWriteReg(RSSI,0x80); //Received Signal Strength Indication

halRfWriteReg(MARCSTATE,0x01); //Main Radio Control State Machine State

halRfWriteReg(VCO_VC_DAC,0x94);//Current Setting from PLL Calibration Module

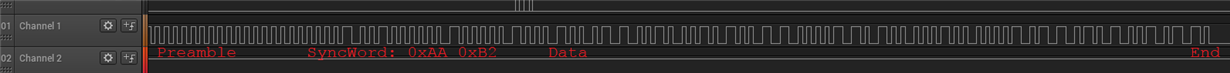

I am trying to recieve signal from keeloq device. I was able to manage to get data in asynchronous mode:

So now some questions:

1. Do i need to use Asynchronous mode ?

I know that i was able to get raw data so i will be able to manage some Teensy handling and timming for demodulation.

2. Is there way how setup Synchronous mode ?

I counted bits several times .. i know that there is PKTLEN register which is in Packets (dont know what exactly mean by packet) than there is a packet count (usually key send data 3times same so one time is one packet ?).

Than there is a FIFOTHR .. this is for setting FIFO Rx data ? in this case is 0x47 ok ? (32 bytes ?).

3. Can you help me setup synchronous mode for RX ?

- There is long preamble - synchronizing bits - from what i underestand more preamble bits better.

- There is sync word - in my program for teensy i already was able to get right interrupts when data was catched in async mode.

- I was not able to get data in sync mode.

- I was not able to get data in sync mode in SmartRF studio.

4. How to calculate data rate ?

I measured signal from transmitter. I know how long is pulse 1 or 0. How do i determine from this time data rate ? I also read that its releated to bandwidth.

Thank you so much for help in advance and sorry for my english ! :)