Tool/software: TI-RTOS

Hello All,

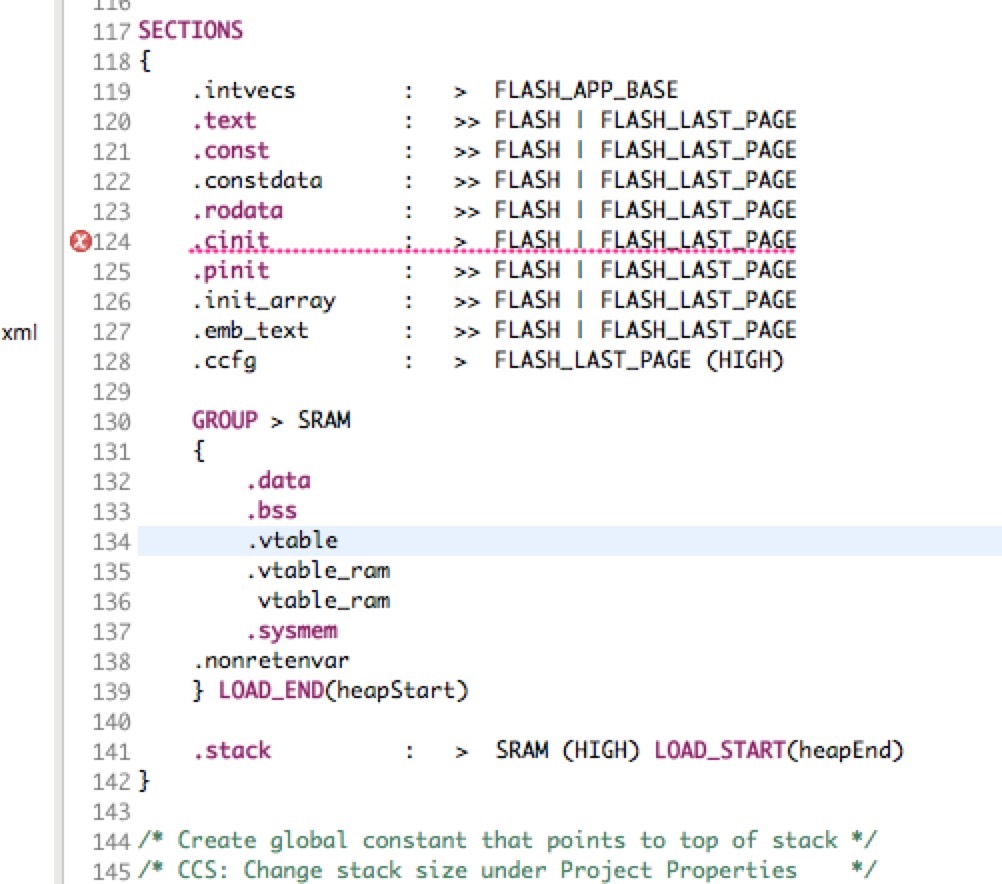

"/Applications/ti/simplelink_cc13x0_sdk_1_60_00_21/source/ti/blestack/common/cc26xx/ccs/cc26xx_app.cmd", line 124: error #10099-D: program will not fit into available memory. placement with alignment fails for section ".cinit" size 0x57e . Available memory ranges:

FLASH size: 0xf000 unused: 0x50e max hole: 0x508

FLASH_LAST_PAGE size: 0x1000 unused: 0x244 max hole: 0x244

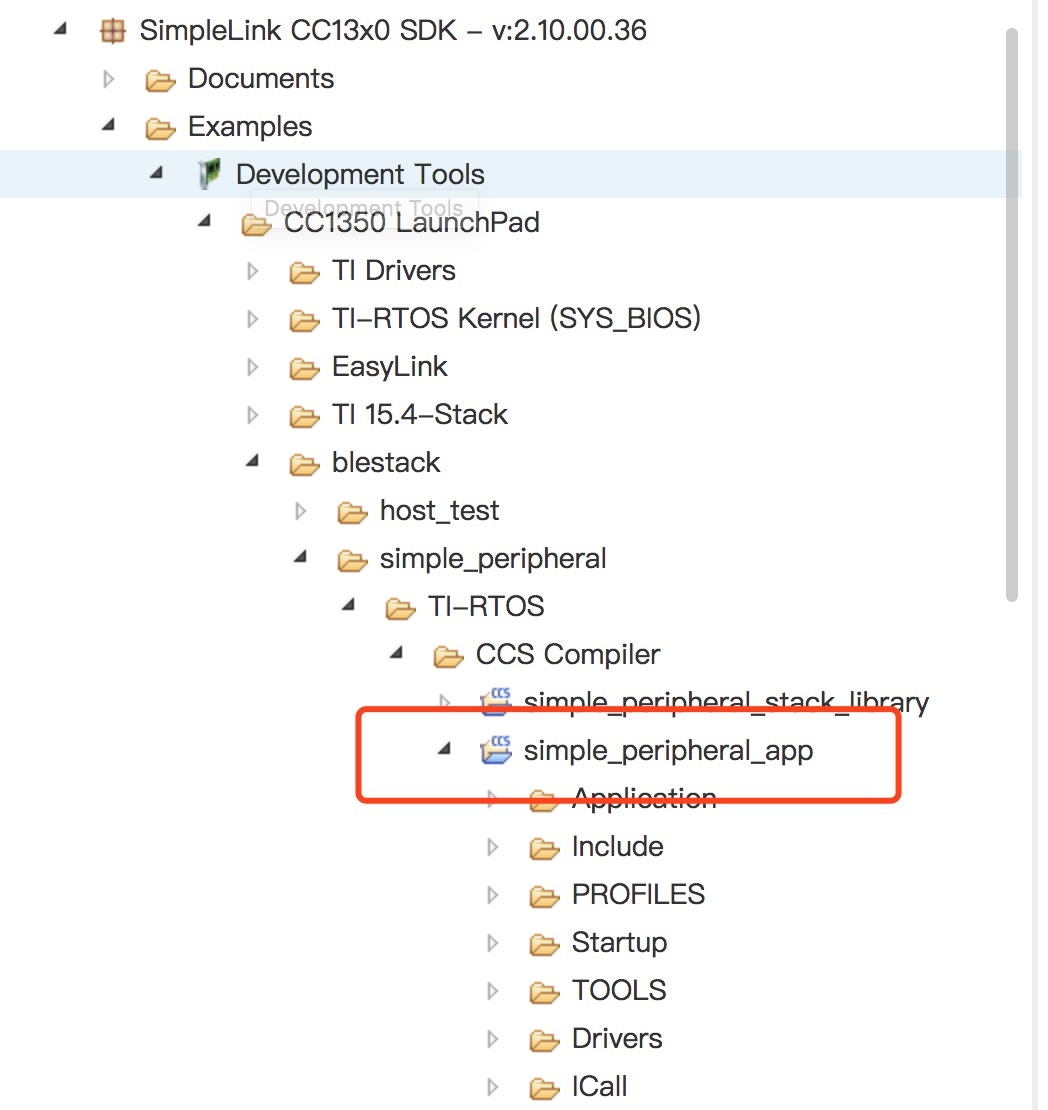

error #10010: errors encountered during linking; "simple_peripheral_cc1350lp_app_FlashROM.out" not built

Can the size of this mapping address be changed?