Other Parts Discussed in Thread: CC1200, CC1310

Does the 1201 require any delay between bytes when writing to the TXFIFO?

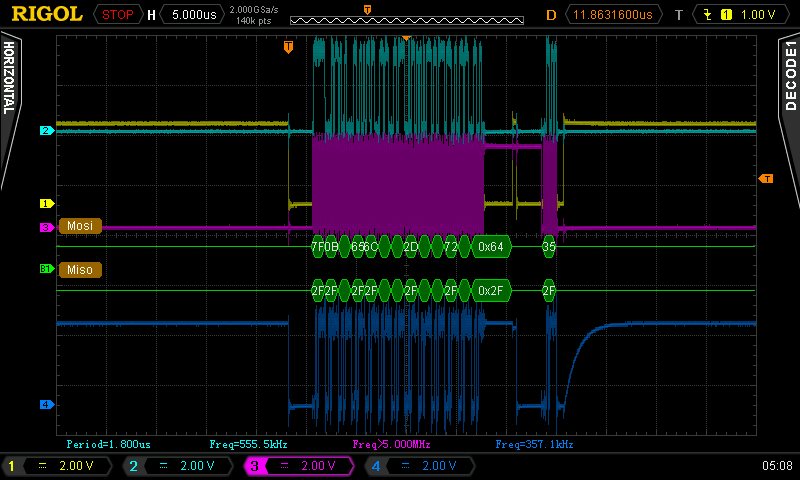

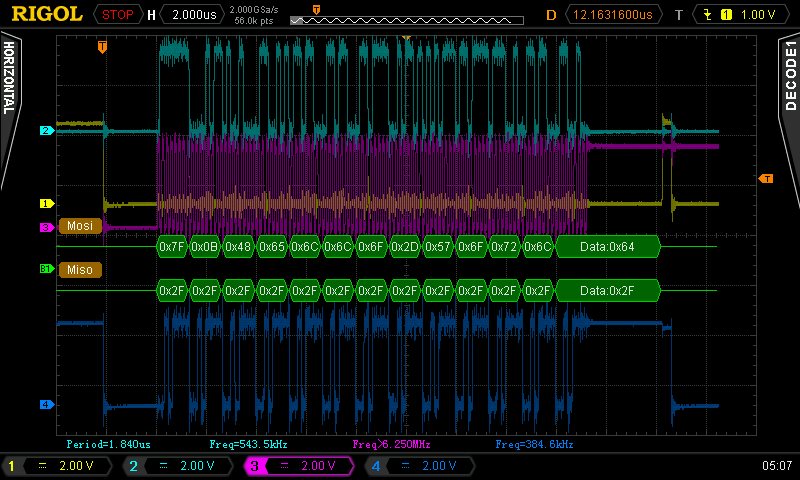

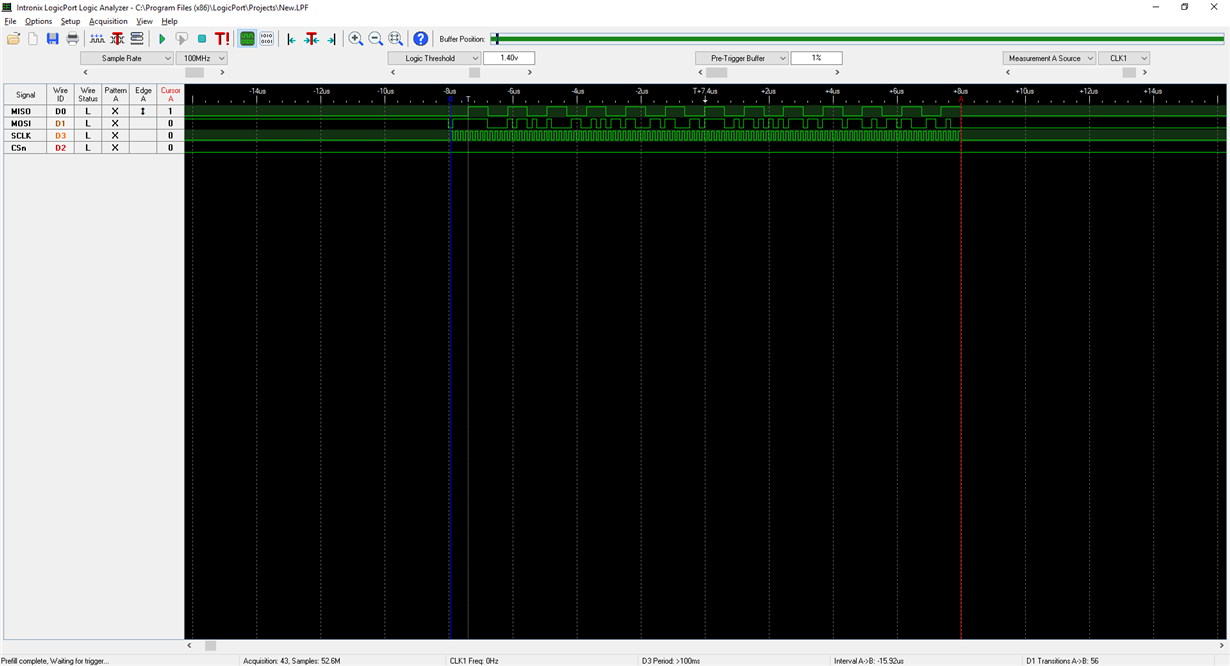

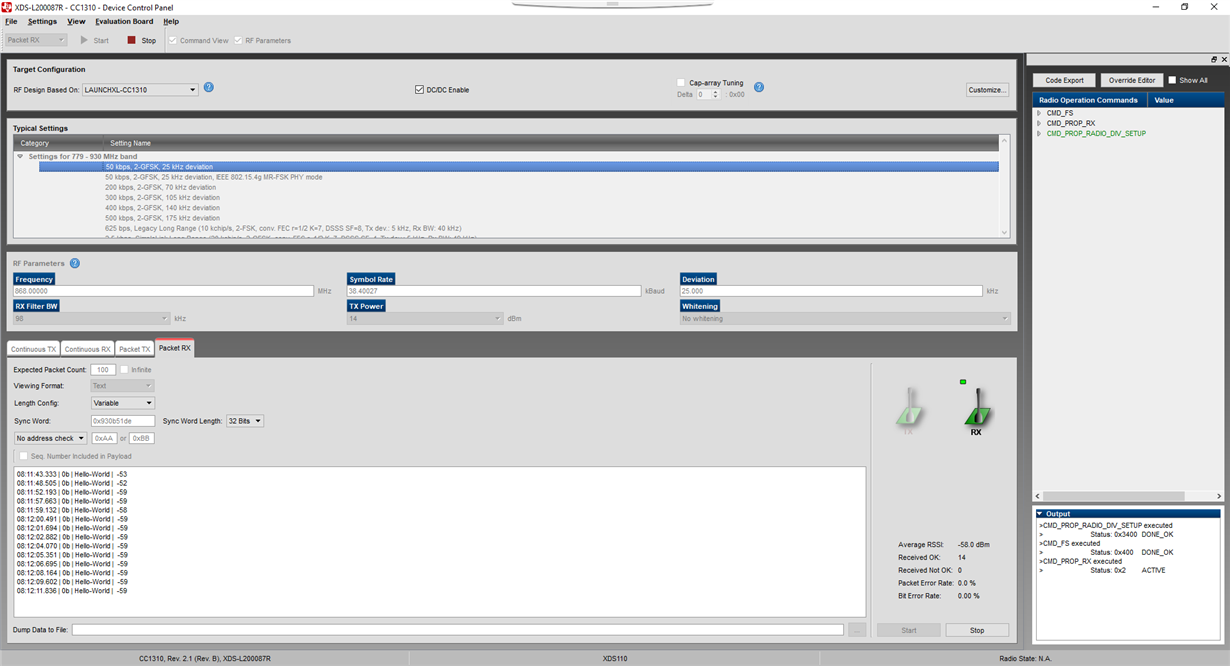

I am running the SPI at 6MHz - if there is a delay between bytes as high as 2uS - then the write is successful. But if the SCLK is continuous - no delay between bytes then it results in a TX Underflow. Device seems to be loosing a byte in the transaction. TXFIFO is being written in burst mode access, and the device is strobed for transmit i.e. the radio is placed in transmit and the FIFO is updated at regular intervals.

User Guide specified a 100ns delay when accessing configuration registers in burst mode - but not for the FIFO.

Thanks - would appreciate any pointers.