Other Parts Discussed in Thread: TPS54240, BQ27441-G1, BQ24074, TPS63051, TPS63020, TPS61099, LP55231, TPL5010, TEST2

We have a rare issue where our cc1310 does not recover after going into standby mode. However the issue does not appear on CC1310 revision A.

We narrowed this problem to uLDO.

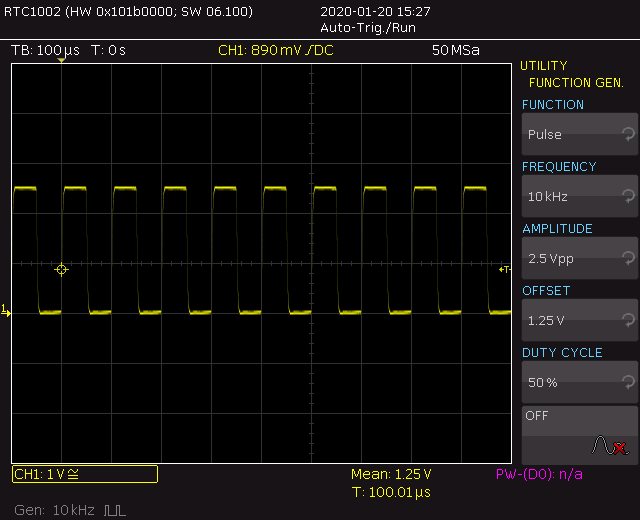

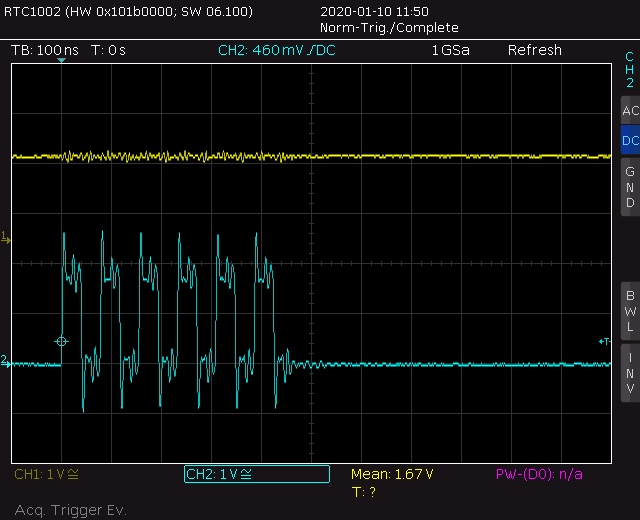

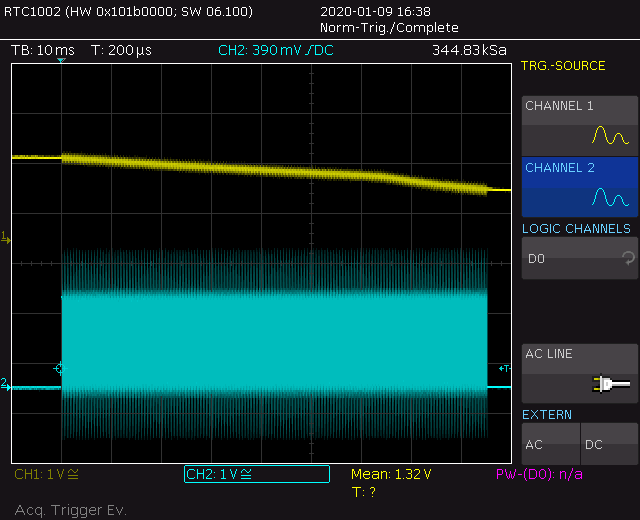

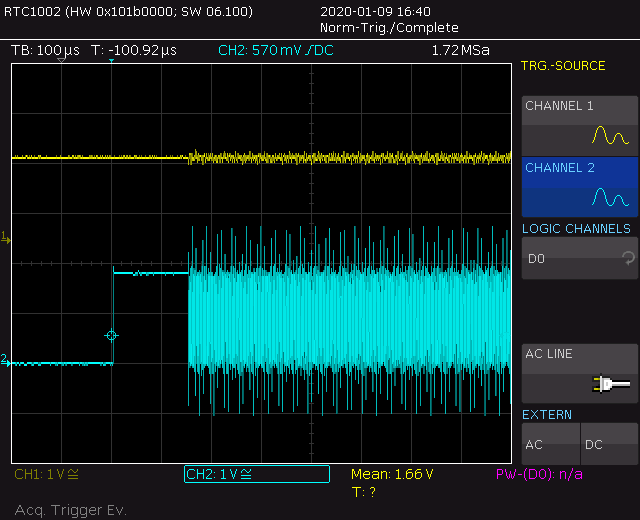

We noticed that when cc1310 is put to standby mode and right after a signal is sent on DIO14 ( signal is square wave, 2.5Vpp 10kHz) voltage on DCDC_SW will drop to 0V and 32kHz xtal will shutdown. to get out of this state cc1310 has to be reseted (done by external watchdog).

If we configure to use digital LDO device is working correctly and never fails. DIO14 is configured as input, pull down. If pin is configured as output system will not fail.

This issue is very severe as we have some units where uLDO is permanently damaged.