We're having trouble with the output power of the 868MHz channel of CC1352R on our board (2-layer PCB).

Tried to run the same code on our PCB and LPSTK-CC1352R - LTSTK outputs 12 dBm when our gives only 6 dBm.

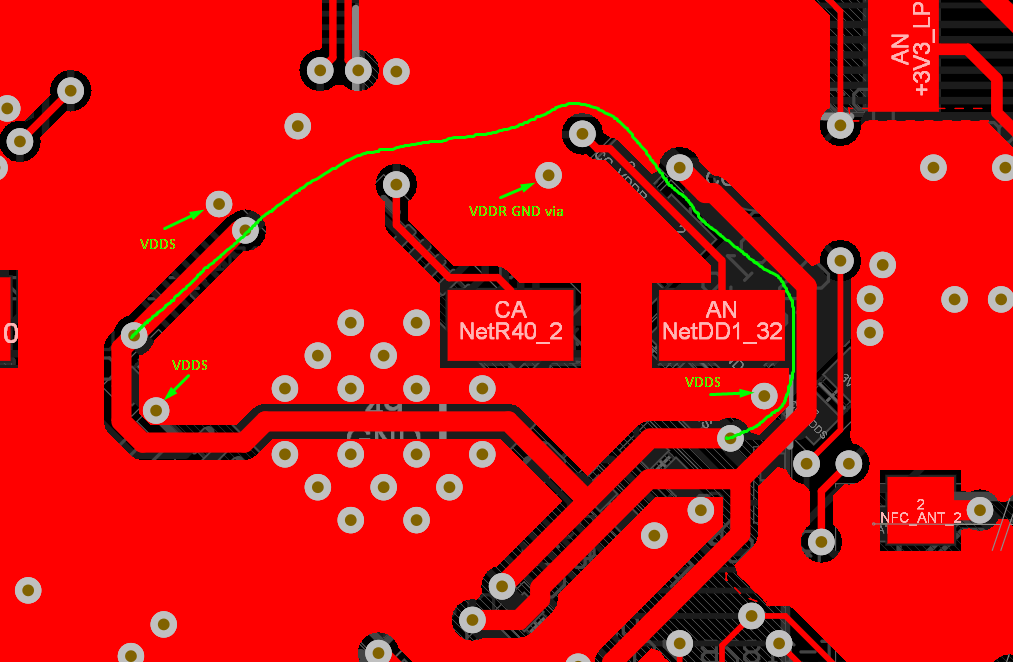

I've found one mistake in the copper - 0900PC15A0036 had a ground poly under its body. Tried to remove it (scratch from the PCB) - same 6 dBm.

Our RF engineer has a suggestion that 0900PC15A0036 can't operate properly on 2-layer PCB, but I didn't found any proofs in the documentation for that.

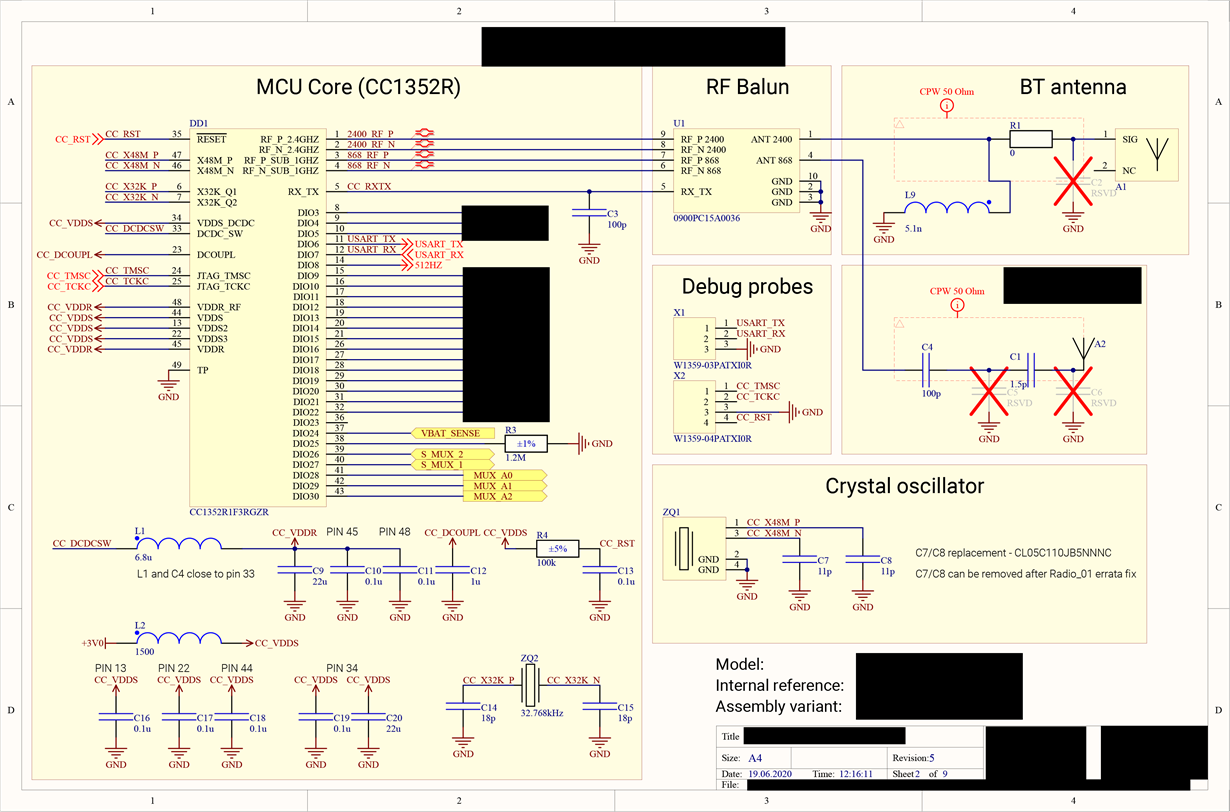

Schematic:

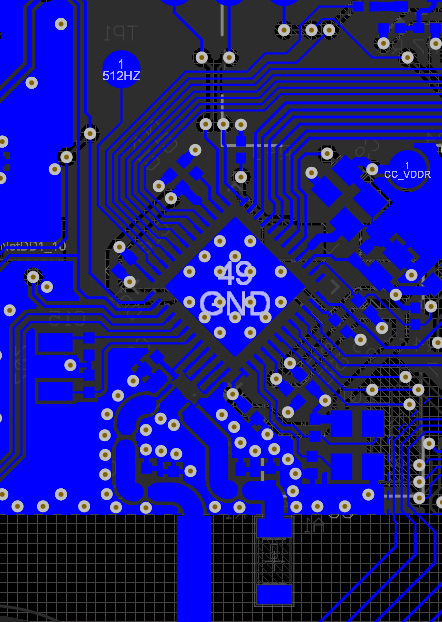

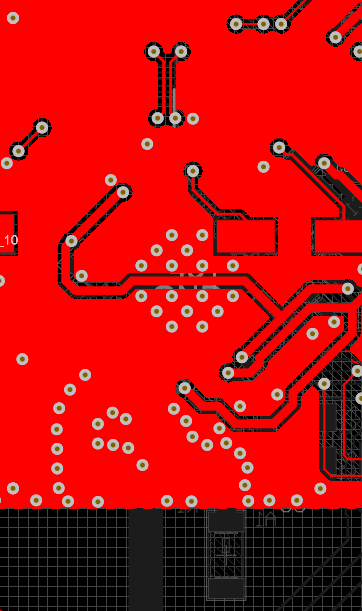

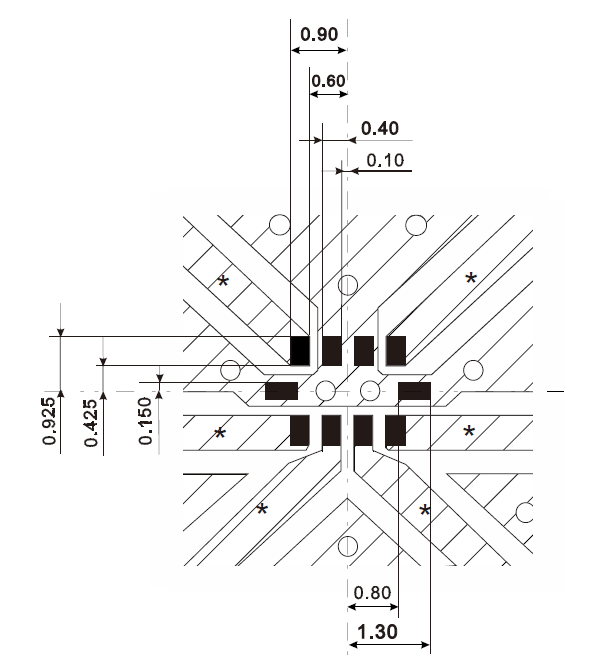

PCB views: