Other Parts Discussed in Thread: CC1310,

Tool/software: Code Composer Studio

Short version: Is it possible to use the I2S driver with a single buffer?

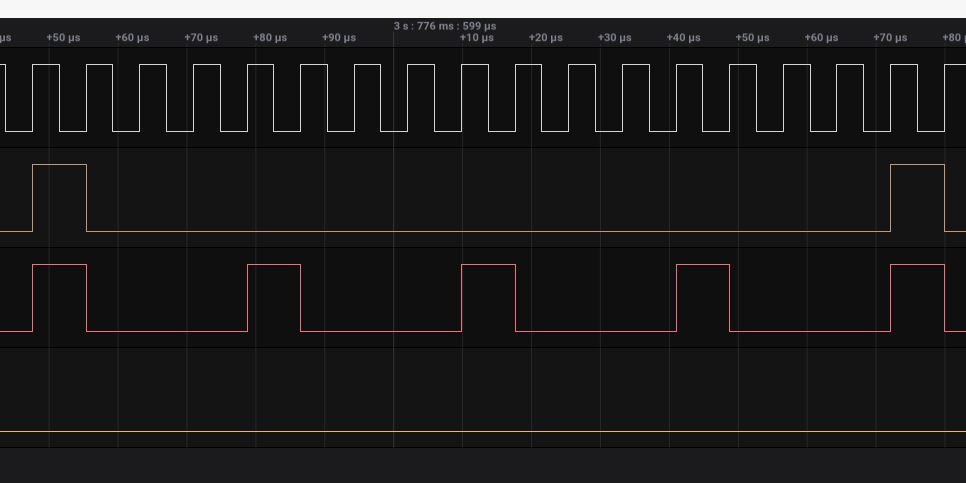

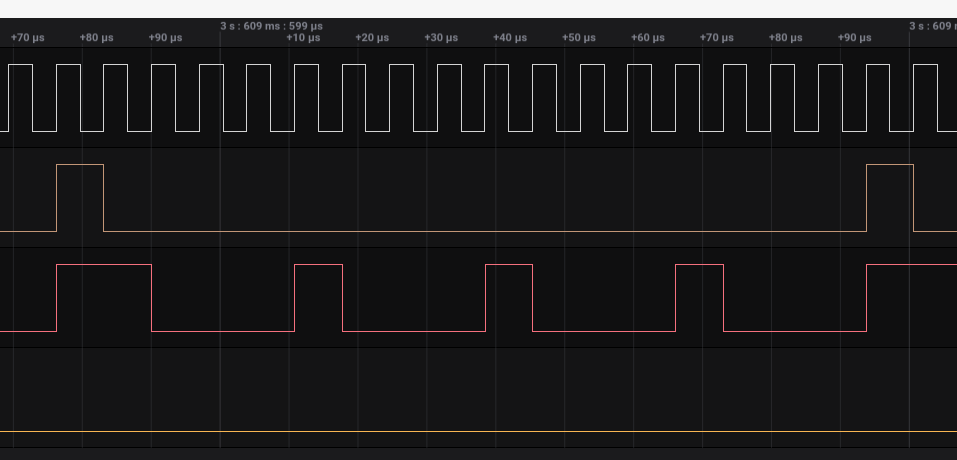

Longer version: I have the following traffic:

I have the following reserved memory:

unsigned char mybuffer[10240];

I have a callback on the posedge of the SIGNAL interrupt and in this callback there are two options:

- either I want to "record" and store the coming 10240 bytes in mybuffer.

- or I don't want to do anything and mybuffer should not be touched.

I would like to avoid any memcpy, to have the minimum of interrupts/callbacks possible and to set fixedBufferLength to 10240.

Question 1: Is it better to stop/start the I2S (with the API I2S_stopClocks(handle); I2S_startClocks(i2sHandle); I2S_startRead(i2sHandle);) or is it better to have it running all the time? (Note that the I2S driver in SLAVE mode).

Question 2: Can I have one single buffer and how to manage it in readCallbackFxn?

Note that I "own" the clock, WS and D0 lanes from a FPGA (for instance, I could have a free-running clock).