Hello,

I am trying to build and SPI slave application on the CC1310 that should behave in the followng manner:

- Master will assert the chip select

- Master transmits 3 bytes

- Delay

- Master transmits rest of the data or clocks to read data from CC1310

The first byte is command, the next to depend on the context.

The idea is that when the master send GET command, followed by two bytes for identifying what data is wants to get, the CC1310 will load that particular data mid transaction (during the delay).

To achieve this I did the following on the slave side:

#define SPI_MSG_LENGTH 0x100

SPI_Handle spiHandle;

SPI_Transaction spiTransaction;

uint8_t spiRxBuffer[SPI_MSG_LENGTH];

uint8_t spiTxBuffer[SPI_MSG_LENGTH];

static void spiInit(void)

{

SPI_Params spiParams;

SPI_init();

SPI_Params_init(&spiParams);

spiParams.frameFormat = SPI_POL1_PHA1;

spiParams.mode = SPI_SLAVE;

spiParams.transferCallbackFxn = spiTransferCallback;

spiParams.transferMode = SPI_MODE_CALLBACK;

spiParams.bitRate = 2000000;

memset(spiTxBuffer, 0, sizeof(spiTxBuffer));

memset(spiRxBuffer, 0, sizeof(spiRxBuffer));

spiHandle = SPI_open(SPI0, &spiParams);

if (spiHandle == NULL)

{

while (1);

}

SPI_control(spiHandle, SPICC26XXDMA_RETURN_PARTIAL_ENABLE, NULL);

memcpy(spiTxBuffer, "123456789ABCDEF", sizeof("123456789ABCDEF"));

spiTransaction.count = 3;

spiTransaction.txBuf = spiTxBuffer;

spiTransaction.rxBuf = spiRxBuffer;

SPI_transfer(spiHandle, &spiTransaction);

}

static void spiTransferCallback(SPI_Handle handle, SPI_Transaction* transaction)

{

bool status;

/* Cancel transfer just in case */

SPI_transferCancel(spiHandle);

if (transaction->status == SPI_TRANSFER_COMPLETED)

{

/* Prepare for second part of transfer */

transaction->txBuf = spiTxBuffer + 3;

transaction->rxBuf = spiRxBuffer + 3;

transaction->count = SPI_MSG_LENGTH - 3;

}

else

{

/* Chip select deasserted. Prepare for new transfer */

transaction->txBuf = spiTxBuffer;

transaction->rxBuf = spiRxBuffer;

transaction->count = 3;

}

status = SPI_transfer(handle, transaction);

}

On the master side I do the following:

- Assert CS

- Transmit 3 bytes

- Delay 1 ms

- Transmit 7 bytes

- Deassert CS

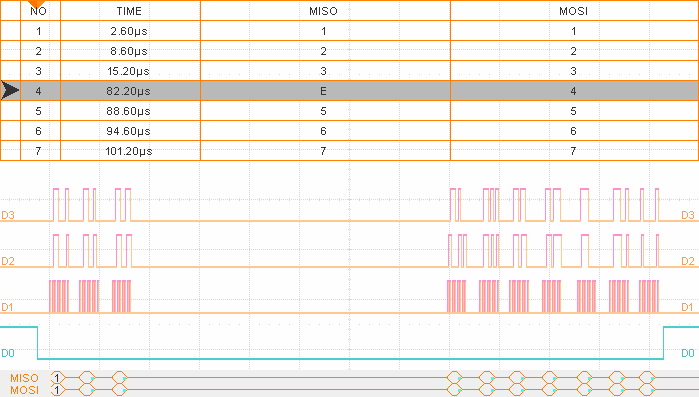

Everything works mostly as intended, with the exception that the 4th bytes I receive on the master side is always corrupted, while there is never a problem with the data received on the slave side.

The first transaction after restarting CC1310 the RX buffer on the master side looks like this:

|

Index |

Data |

|

[0] |

‘1’ |

|

[1] |

‘2’ |

|

[2] |

‘3’ |

|

[3] |

‘1’ |

|

[4] |

‘2’ |

|

[5] |

‘3’ |

|

[6] |

‘4’ |

|

[7] |

‘5’ |

|

[8] |

‘6’ |

|

[9] |

‘7’ |

After the second transaction, the master RX buffer looks like:

|

Index |

Data |

|

[0] |

‘1’ |

|

[1] |

‘2’ |

|

[2] |

‘3’ |

|

[3] |

‘B’ |

|

[4] |

‘5’ |

|

[5] |

‘6’ |

|

[6] |

‘7’ |

|

[7] |

‘8’ |

|

[8] |

‘9’ |

|

[9] |

‘A’ |

For all other transactions, the master RX buffer looks like:

|

Index |

Data |

|

[0] |

‘1’ |

|

[1] |

‘2’ |

|

[2] |

‘3’ |

|

[3] |

‘E’ |

|

[4] |

‘5’ |

|

[5] |

‘6’ |

|

[6] |

‘7’ |

|

[7] |

‘8’ |

|

[8] |

‘9’ |

|

[9] |

‘A’ |

I am using simplelink_cc13x0_sdk_1_60_00_21 and CCS Version: 10.1.0.00010.

I would appreciate your help with the issue. Thank you,

Borislav