I'm trying to find the root cause of a first time boot issue we are seeing with the CC3220MODSF on our boards.

Summary: The board is assembled with an unprogrammed module. In production test the serial flash (in the module) is the programmed while reset is kept active low and when the programming is done the reset is de-asserted. After a delay to allow the module to boot, some commands are sent to the Wi-Fi module to check that it's alive. For simplified testing I have used two commands, one to read out the MAC address and one to Clock_getTicks() done in a loop with some delay between each operation. It's then a finite probability that Wi-Fi module will not respond. Meaning running the same test 100 times on a board a variable percentage of the tests will fail.

More details:

The serial flash is programmed through SPI as described in chapter 4 in swra568. The programming is done through test needles. When the programming is done the buffer is set in high-z.

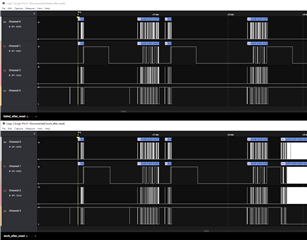

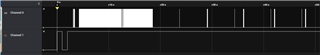

I have monitored the SPI bus when the reset to the module is de-asserted. Channel0 is flash_spi_clk and channel1 is reset. This is typically happens when the module is not responding:

The SPI bus is active for 2.5 ms meaning that the content of the serial flash is never read.

For this cases I found that doing an extra reset helps:

The first 2.5 ms on the SPI bus is exactly the same as for the first picture. The SPI bus pulses seen after first time boot is when the MAC address is read out. The "Clock_getTicks()" will return 0x6 every second time.

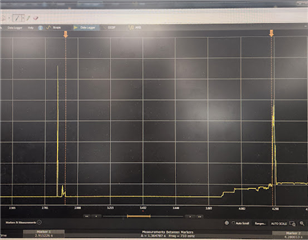

Inserting a 3. reset:

the module returns an expected Clock_getTicks() value each time it's called and no traffic on the SPI bus when reading out the MAC address.

Could someone explain why the Wi-Fi module needs an extra reset to boot in some cases? If the reset time is too short it also fails.