Other Parts Discussed in Thread: CC3235SF, CC3220SF, SYSCONFIG

Tool/software:

After producing a run of hardware for a new design, we discovered a small oversight in the design we're hoping to fix in firmware without having to modify the hardware.

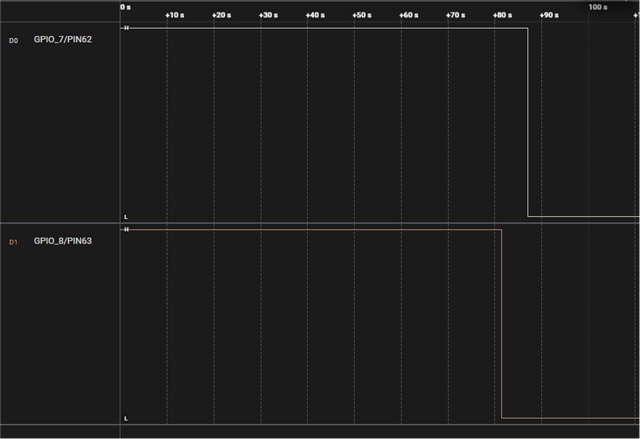

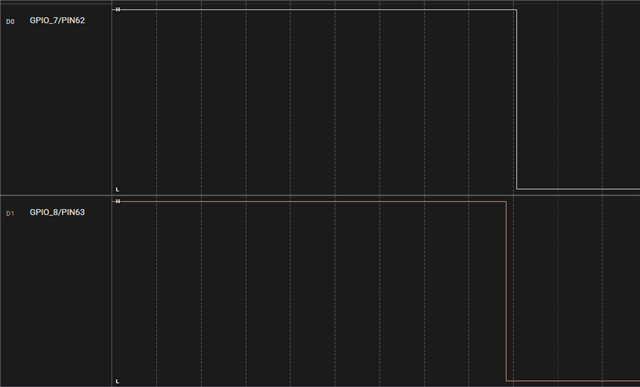

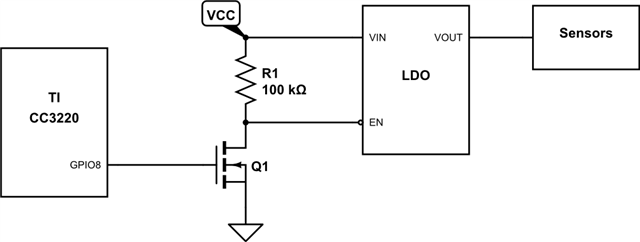

This system primarily stays in hibernate mode but wakes up a few times per hour to take some sensor measurements. Power management for these external sensors is handled by simply turning off their dedicated power supply.

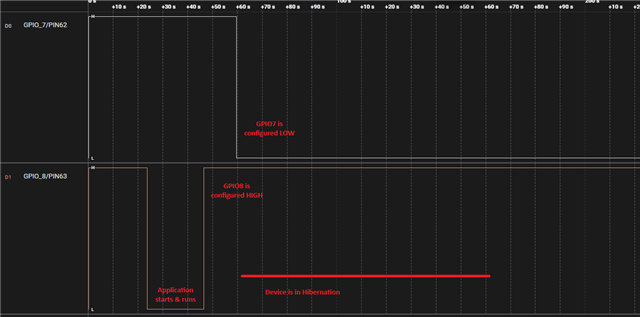

We accidentally omitted the external pull-down on the gate of Q1 necessary to guarantee that the LDO and sensors stay off when the CC3220 is hibernating and GPIO8 is hi-Z. So we're seeing some unpredictable behavior as GPIO8 floats randomly while the CC3220 hibernates.

Reading the CC3220 datasheet and manual, it seems like we should be able to fix this with only firmware by making sure we do the following:

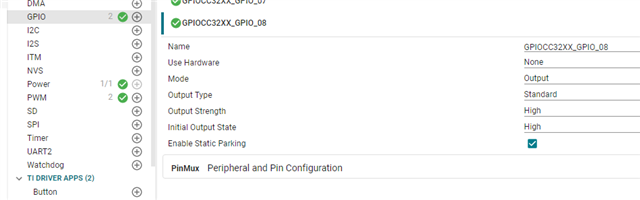

- Configure IO retention to include retention group #0, which (of the four groups) is the group containing GPIO8

- Before hibernating, and immediately before activating IO retention, (re)configure GPIO8 as an input with internal pull-down enabled

- After reconfiguring GPIO8 as input w/PD, but before hibernating, activate/enable IO retention

- Enter hibernate mode, where the pulled-down state of GPIO8 should be retained for the entire hibernation period

This is our understanding, but after taking a crack (or five) at it ourselves we're not having much success getting the desired result.

Can TI confirm...

- That it should be possible to resolve this "missing external pull-down causing random behavior during hibernate" issue with only a firmware update?

- Whether we're missing (or misunderstanding) any critical steps to get this to work as expected?

- Any common pitfalls/gotchas/drawbacks to using this IO retention functionality?