Tool/software:

Hi team,

My customer would like to ask about the SPI.

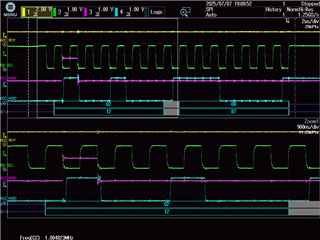

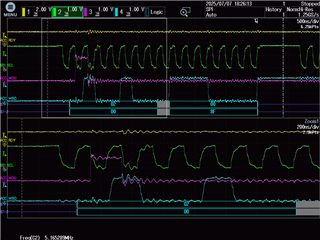

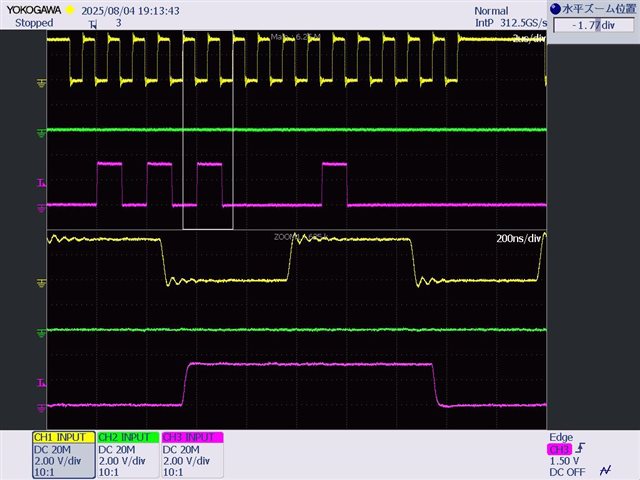

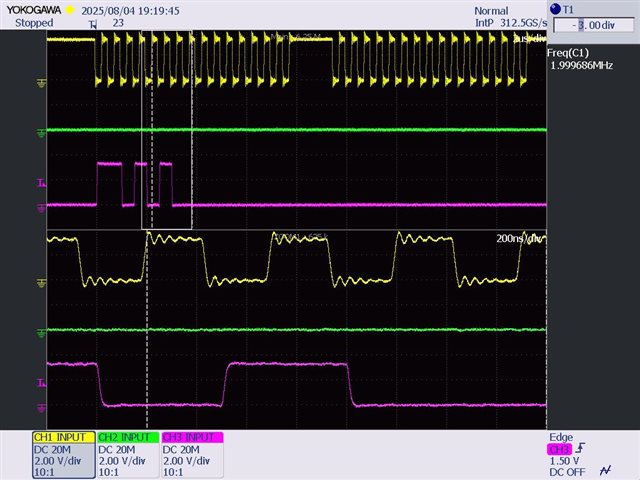

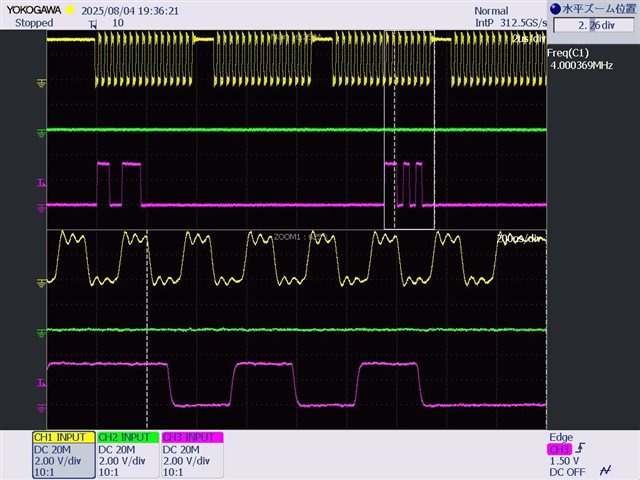

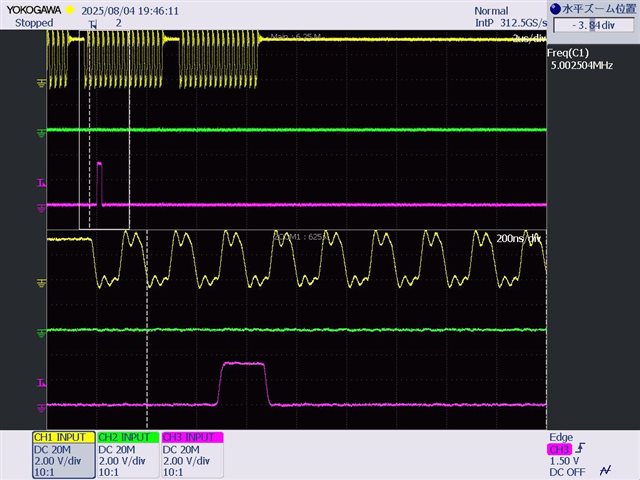

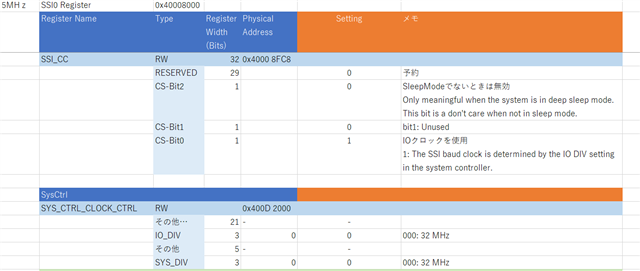

The cc2538 is used as a slave for SPI communication, but there is a problem when communicating at 5MHz.

The attached User’s Guide does not seem to describe the setup/hold time for SPI communication (19.4.4.2+).

On the other hand, there is a description of MicroWire (Figure 19-12.), is it the same as here?

It would be appreciated it if you could send us any documentation on timing characteristics such as setup/hold time of SPI communication.

Best regards,

Kenley