Other Parts Discussed in Thread: CC3301

Tool/software:

Hi All,

There is little documentation available for CC3301MOD, so please provide details on its specifications.

1. Interrupts

https://www.ti.com/jp/lit/an/swra779/swra779.pdf

・It is unclear when interrupts occur.

・It is unclear how to obtain interrupt factors.

・It is unclear whether interrupts can be masked.

2. Cmd, Addr

• The detailed format of CMD and Addr is unclear.

• In the above documentation, Addr appears to be 16 bits, but in the sample project, it appears to be 17 bits.

• The list of CMDs is unclear.

• The specifications for Addr are unclear (does the value of Addr depend on the CMD?).

3. Protocol Structure

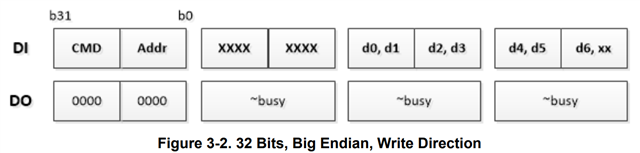

・Does the above Protocol Structure correspond to the data section (d0, d1, ... d6, xx) in Figure 3-2?

・The specifications for SYNC are unclear (size, fixed value, but the specific value)

・The specifications for Opecode are unclear (size, list of Opecodes)

・The format appears to differ from the sample project. We would like to know the correct specifications.

After initial processing is complete, the specification states that firmware is downloaded from the host to the CC3301MOD.

We have confirmed that the above flow is implemented in the sample project.

4. Firmware Download

・Is this download process required every time the power is turned on?

Is it not possible to save the firmware to CC3301?

For example, is it not possible to download and save the firmware to CC3301 only once initially, and then continue to operate with the downloaded firmware even after a power restart?