Tool/software:

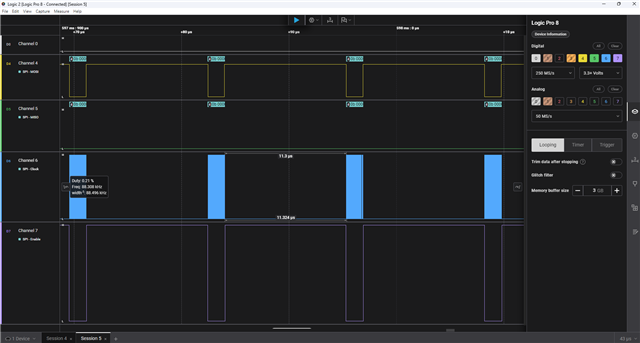

We have an external ADC that provides 32bit data (2 back to back 16bit values) back over SPI. There is a driver level delay that limits us to about 30us between samples. We have looked a few times at using a timer to Trigger the SPI to transfer data via DMA into memory. We have not been able to figure this out. It seems that some details in the datasheet are not fully worked out. There are some "signals" that should be able to do the triggers, but it is not clear how to fully map the setup. Some details are called out in descriptions of setup, but then not found in register map details.

It might be that it is not possible but would like to check with those that have deeper knowledge before we totally give up. We are currently using a PWM to trigger the ADC. This allows us to adjust the timing as we need to change when we need samples. The goal of using the DMA would be to load data directly into memory and then use CPU cycle to check if we want to keep data or skip data. Also if we could get down to about 5us between samples that would be useful. 10us would be workable.