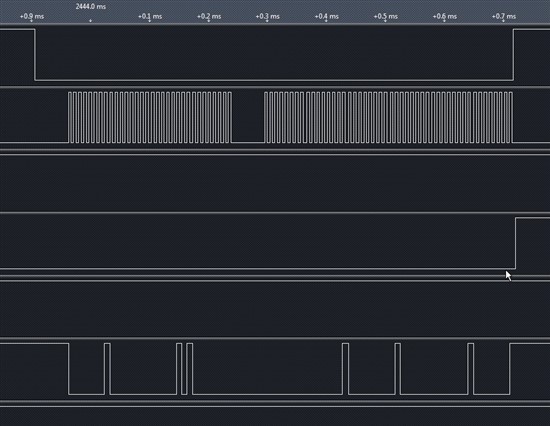

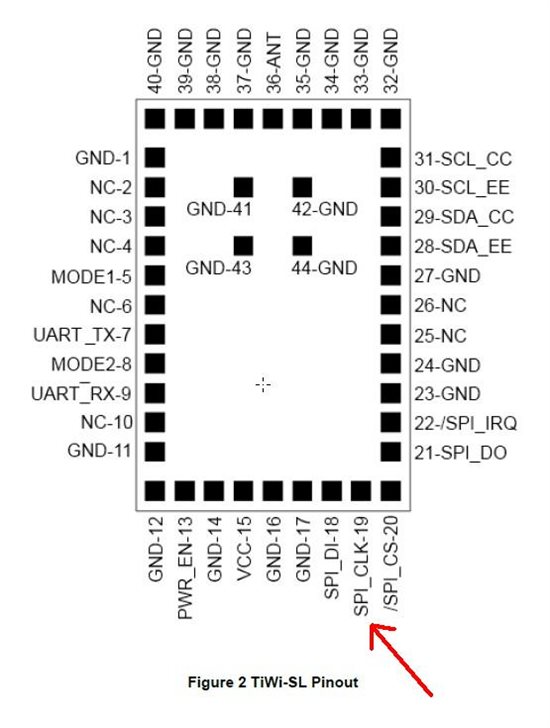

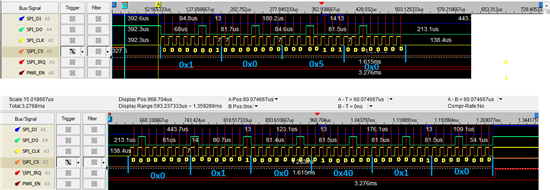

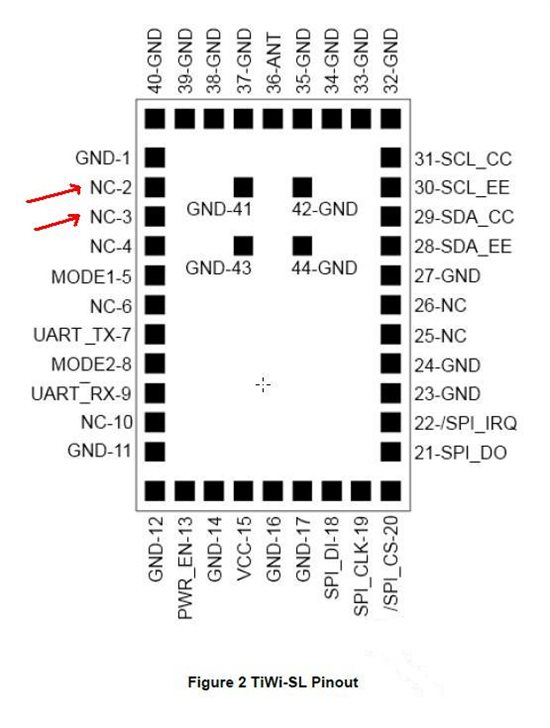

Greetings. I am using a TiWi-SL REV2, and have everything hooked up to the logic analyzer. I have verified that my initial sequence of PWR_EN high, wait for IRQ to go high, wait for IRQ to go low, Drop CS, wait for IRQ to go low, delay, Write out: 0x01 0x00 0x05 0x00, delay, 0x00, 0x01, 0x00, 0x40, 0x01, 0x00...raise CS , verify that IRQ raises, and then I'm supposed to wait for IRQ to drop low again which is indicating that the device is trying to send data.

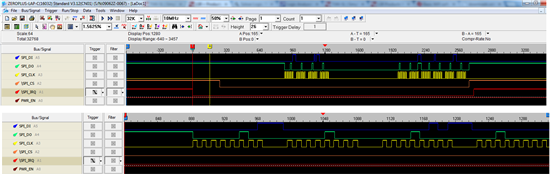

I never get this final IRQ drop. I verified with a logic analyzer that the data is setup on the rising edge and sampled on the falling edge, that it is transmitting the MSB first, and that all the timings look correct.

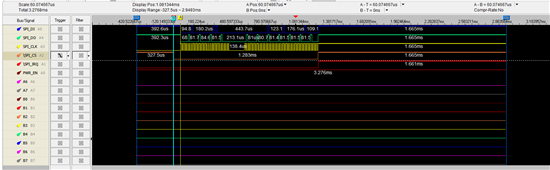

What's strange is that I've seen other people's logic analyzer captures, and the values that are getting written on the MISO line from the device do not match what I see in other people's logic analyzer. (it's usually like 0x02, 0x00, 0xfe, etc, etc in other people's, but mine is more like 0x04, 0x08, 0x10, 0x20...like a shifting bit position).

Did anyone else have this problem or does anyone else have any suggestions on what may be the issue? I'm running low on ideas