Hello,

I am working on porting host driver of cc3000, and I have a question about its initialization. I actually have submitted this question to TI FAE, and is awaiting for their response. But I was wondering whether anybody here could help answer it in the mean time so that I can get it around soon.

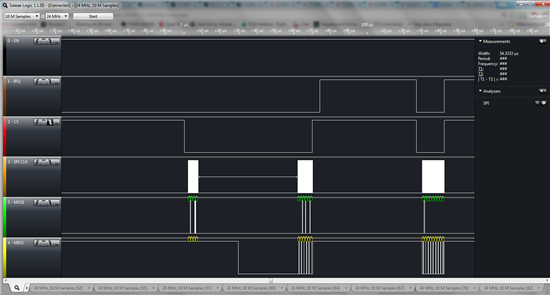

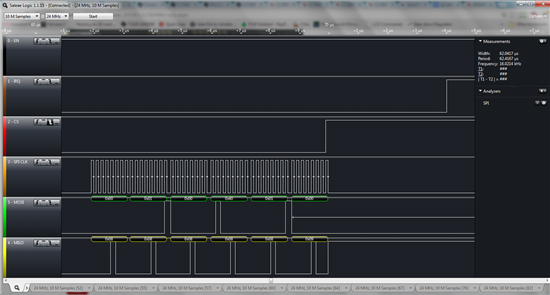

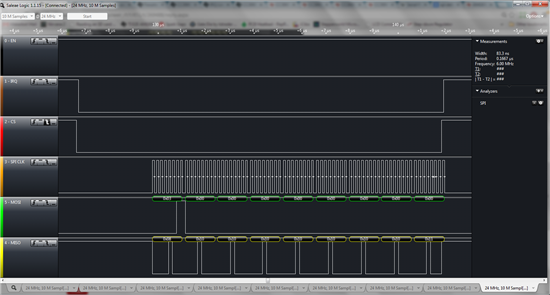

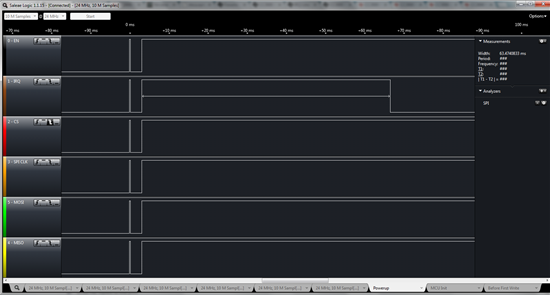

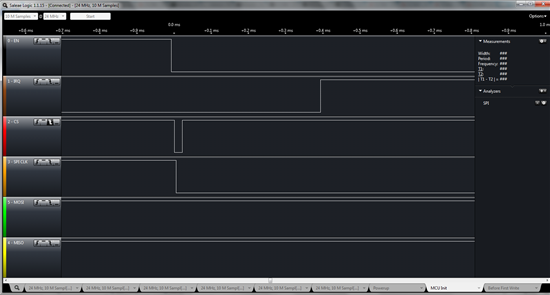

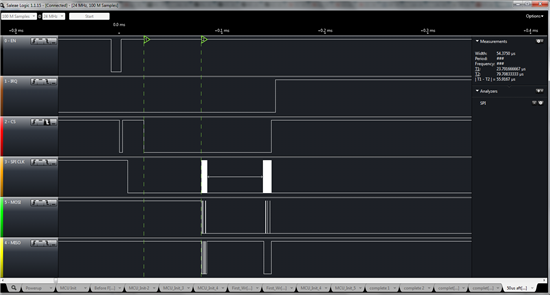

My question is about SPI timing requirement of CC3000. Since the authentic SPI in the MCU is used for other purpose, I am using general purpose IOs to emulate SPI. Then I was getting problem of initialization, especially on the first write, as many others did. The logic of first write to CC3000 is attached for your reference. I was getting data on MISO before the finish of first write. Also all the subsequent data I received on this line later didn't make sense. Thus I were wondering whether it has something to do with SPI timing, as I was not using the authentic interface.

In Table 4 (page 8) of CC3000's datasheet, it requires the pulse width of SPI clock line to range from 25 to 37.5 nanosecond. For now the shortest pulse we can achieve with GPIO in CCS is only 0.33us, and we could possibly reduce it further by using assemble language in the source codes. But we are afraid we cannot decrease that to an order of 10 to reach 37.5ns target.

Is that true that requirement has to be met? I have seen some people online using SPI clock frequency of 6MHz to communicate with CC3000, and I don't think that clock speed will lead to the pulse width of 37.5ns.

Please advise.

Thanks,

Dawei