Hello.

I'm using the CC3200, and I see intermittent problems with the I2C CLK signal. I haven't seen it with 100kHz, but it is present with 400kHz and 300kHz. It happens often enough that it's repeatable, but it doesn't always fail.

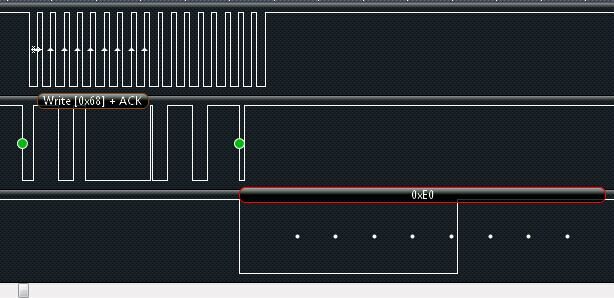

Please see attached screenshot of the scope.

I'm using the CC3200 as the master. I'm doing a transmit to address 0x21, so the first byte is 0x42 when you add on the '0' at the end for transmit. There are two attempted I2C transmissions in the screen shot. In the first byte, pulse 6 of the CLK (yellow/top signal) is short for some reason. Because the slave device doesn't see this as a pulse of the Clock, it doesn't ACK this transmission. You can see that I try to start the message again, but this time it's the first pulse of the CLK that causes the problem. The TI CC3200 counts those short pulses in it's 9 clock pulses per byte, but the slave device does not - so there is no ACK.

Why are these short pulses present?

I'm using TI's library code and code from the I2C demo almost exclusively.

I2C_IF_Open(I2C_MASTER_MODE_FST);

//using the I2C write function provided by the TI demo code.

//all I2C commands use address = 0x21, length = 2 and stop = true.

ucDevAddr = (unsigned char)0x21;

ucLength = (unsigned char)2;

ucStopBit = (unsigned char)true;

//send pixel clock divisor message to clock addr: 0x42, register: 0x11, data: 0x1F

aucDataBuf[0] = (unsigned char)0x11;

aucDataBuf[1] = (unsigned char)0x1F;

i2cErrorReported = I2C_IF_Write(ucDevAddr, aucDataBuf, ucLength, ucStopBit);