Hello,

I would like to know what changes in the "wifi audio app" example I have to do to run it at 48k, still 16bit.

I have a CC3200 launchpad with a Audio booster pack on it.

I tried to modify the code in the AudioCodecConfig() and AudioCaptureRenderConfigure() functions.

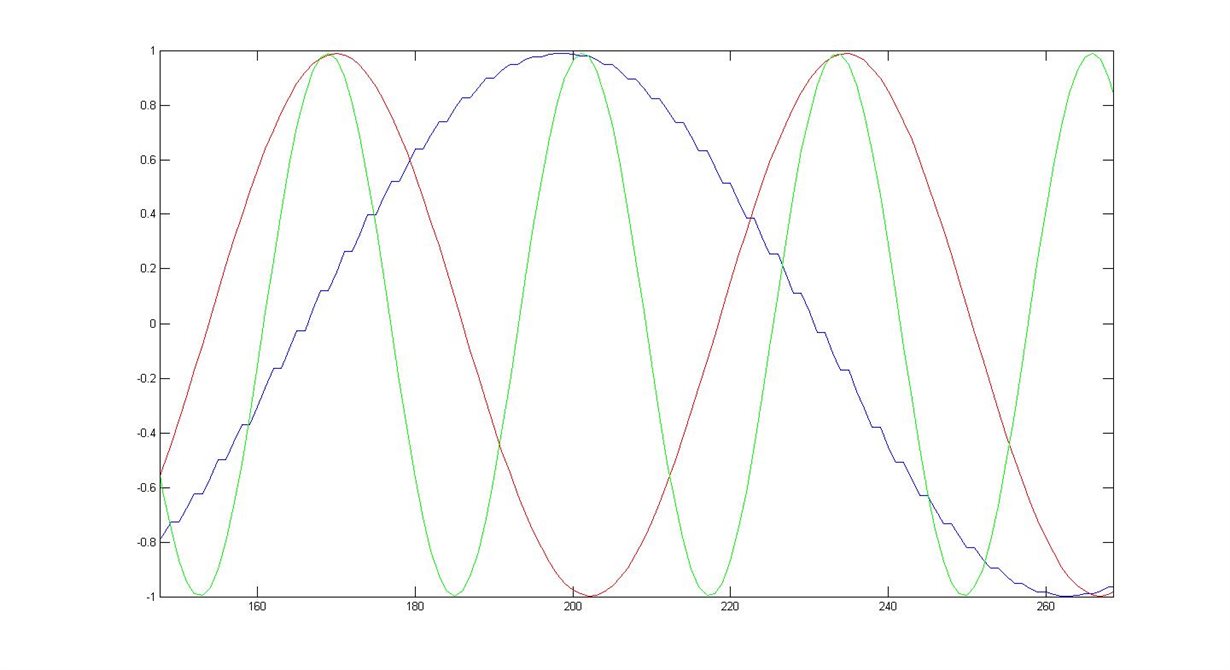

Then I tried to send an simple frequency wave through the module and get the data in matlab.

This method works great at 16k/16bit (the default configuration of the wifi audio app), but at 48k the wave I get is very weird and awful. (I can post a picture of it if necessary) .

Here are the changes I made so far :

- for the AudioCaptureRenderConfigure() function :

how I call it :

AudioCaptureRendererConfigure(AUDIO_CODEC_16_BIT, 48000, AUDIO_CODEC_STEREO, RecordPlay, 1);

The changes I made :

if((bitsPerSample == 16)&&(bitClk==1536000))

{

MAP_PRCMI2SClockFreqSet(1536000);

MAP_I2SConfigSetExpClk(I2S_BASE,1536000,bitClk,I2S_SLOT_SIZE_16|

I2S_PORT_DMA);

}

- for the AudioCodecConfig function :

how I call it :

AudioCodecConfig(AUDIO_CODEC_TI_3254, AUDIO_CODEC_16_BIT, 48000,

AUDIO_CODEC_STEREO, AUDIO_CODEC_SPEAKER_ALL,

AUDIO_CODEC_MIC_LINE_IN);

the changes I made :

if(bitClk == 1536000) //48k st

{

AudioCodecPageSelect(TI3254_PAGE_0);

AudioCodecRegWrite(TI3254_CLK_MUX_REG, 0x03); // PLL Clock is CODEC_CLKIN @ 768.000

AudioCodecRegWrite(TI3254_CLK_PLL_P_R_REG, 0x94); // PLL is powered up, P=1, R=4

AudioCodecRegWrite(TI3254_CLK_PLL_J_REG, 0x2A); // J=42

AudioCodecRegWrite(TI3254_CLK_PLL_D_MSB_REG, 0x00); // D = 0

AudioCodecRegWrite(TI3254_CLK_NDAC_REG, 0x87); // NDAC divider powered up, NDAC = 7

AudioCodecRegWrite(TI3254_CLK_MDAC_REG, 0x82); // MDAC divider powered up, MDAC = 2

AudioCodecRegWrite(TI3254_DAC_OSR_MSB_REG, 0x01); // DOSR = 0x0180 = 384

AudioCodecRegWrite(TI3254_DAC_OSR_LSB_REG, 0x80); // DOSR = 0x0180 = 384

AudioCodecRegWrite(TI3254_CLK_NADC_REG, 0x95); // NADC divider powered up, NADC = 21

AudioCodecRegWrite(TI3254_CLK_MADC_REG, 0x82); // MADC divider powered up, MADC = 2

AudioCodecRegWrite(TI3254_ADC_OSR_REG, 0x80); // AOSR = 128 ((Use with PRB_R1 to PRB_R6, ADC Filter Type A)

}

Thanks in advance.

Nicolas