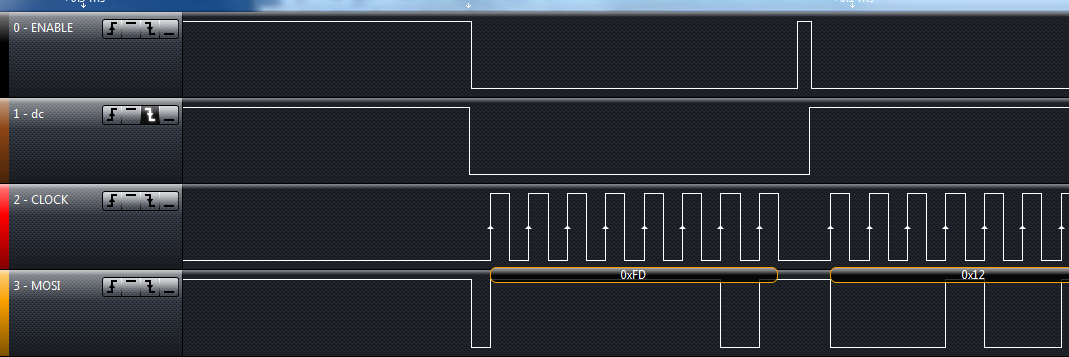

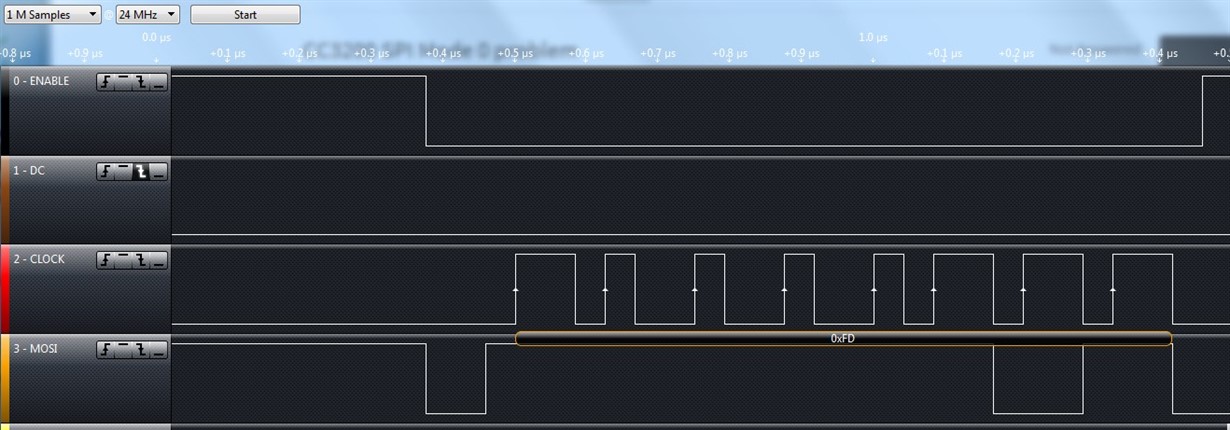

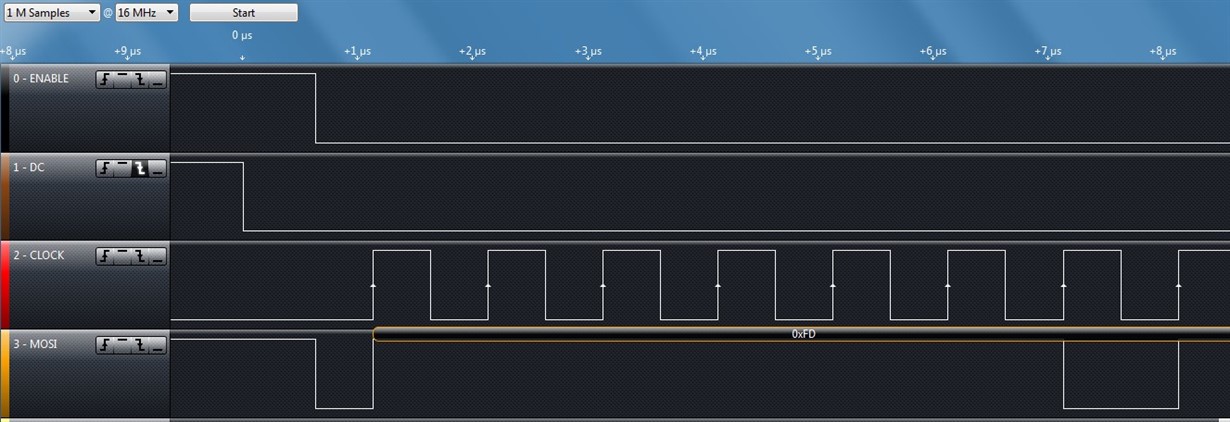

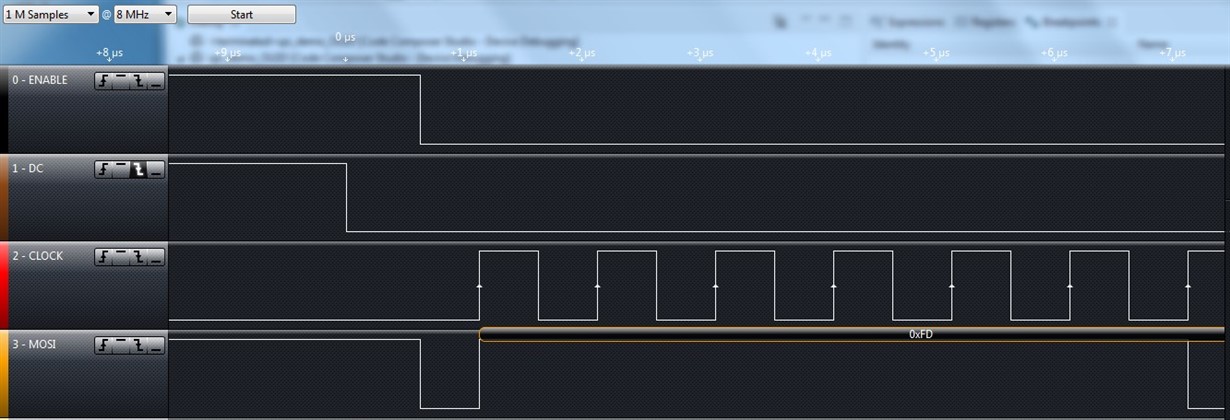

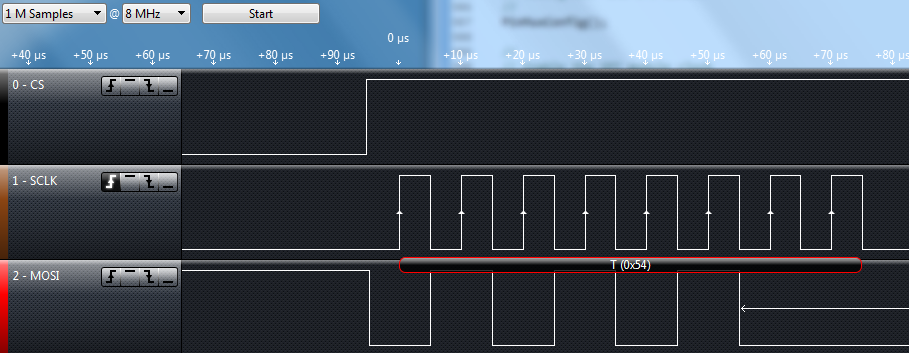

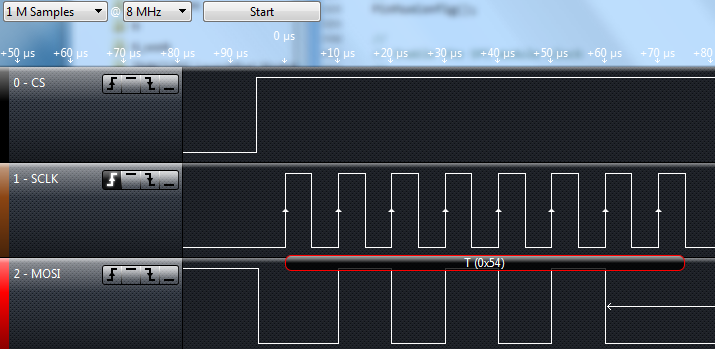

I'm interfacing to an OLED using the CC3200 SPI port. The CC3200 seems to output incorrect signals in Modes 0 and 2. The data (MOSI) should be asserted when the SPIEN goes active, but instead it is asserted on the first clock edge, which is also when the data is sampled when PHA=0. Modes 1 and 3 work correctly because the MOSI data is asserted on the first clock edge and sampled on the second as expected when PHA=1. I've verified this with a logic analyzer on 2 different CC3200 LauchPads.

You can see in the screenshot that the MSB is not asserted when ENABLE goes low, but when CLOCK goes high. This is when data should be sampled in Mode 0. I'm using the following command to configure the SPI:

SPIConfigSetExpClk(GSPI_BASE,PRCMPeripheralClockGet(PRCM_GSPI),

SPI_IF_BIT_RATE,SPI_MODE_MASTER,SPI_SUB_MODE_0,

(SPI_HW_CTRL_CS |

SPI_4PIN_MODE |

SPI_TURBO_OFF |

SPI_CS_ACTIVELOW |

SPI_WL_8));

I've successfully used Mode 0 with this OLED using a Tiva LaunchPad and a Stellaris LM3S8962 Evaluation Kit. Fortunately, Mode 3 works with the CC3200 LaunchPad. This Mode 0 problem seems like a hardware bug to me. Has this been seen before?