Other Parts Discussed in Thread: CC3100

Dear all,

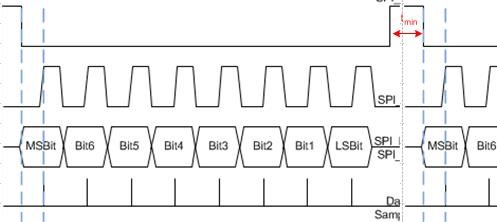

my customer is trying to connect the CC3100MOD via SPI to a host MCU and is facing SPI communication issues when switching off the CC31xx SPI Debug feature. Adding a delay of ~1ms between each SPI telegram, it seems to work again.

Questions are:

Are there specific timing requirements defined between SPI telegrams?

Are there any error handling mechanisms implemented on the SPI-host drivers, to recover from erroneous telegrams?

Thanks,

BR,

Matthias