Other Parts Discussed in Thread: TXS0108E, AM3359

Tool/software: Linux

Once again trying to get a custom module with WL1837MOD working, now that the new hardware came in.

I am using BeagleBone Black as the reference platform. We took a board we designed previously for testing which was able to operate properly at reduced MMC clock speed. The main difference between the new board and the one we were able to make work is in the voltage regulators (for 3.3V and 1.8V). The previous design has onboard regulators similar to TI reference designs, whereas the new board is relying on off-board regulators...in fact both the 3.3V and the 1.8V supplies for the WL1837MOD are coming straight off the TPS65217C in the new design (LS2_OUT and LS1_OUT, respectively).

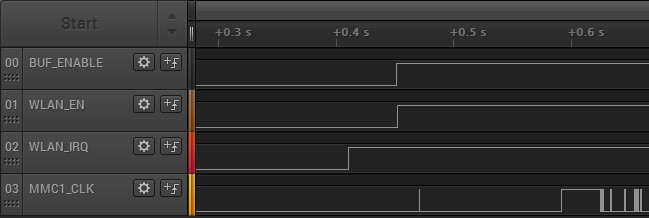

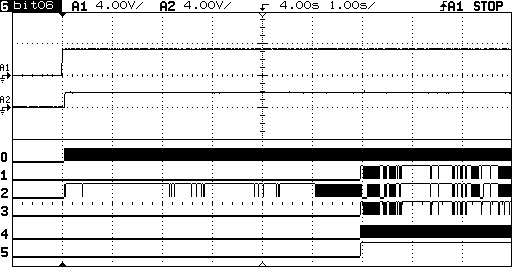

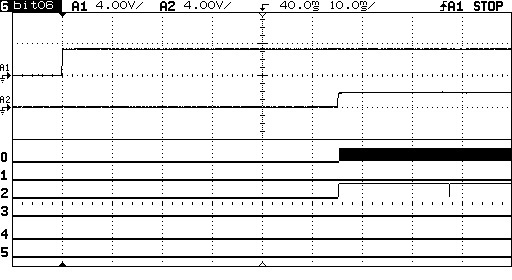

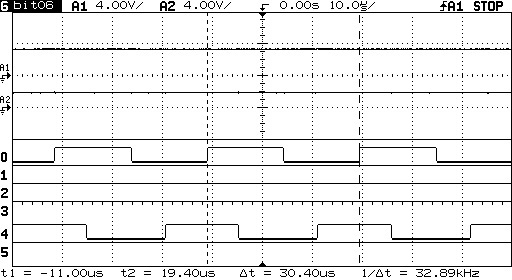

I have verified the BUF_ENABLE and WLAN_EN are matching the same startup sequence for both the reference board (the element14 WiFi cape) and our new board. However, on the working reference board, the WLAN_IRQ signal goes low about 19ms after the WLAN_EN goes high. But on our board, the WLAN_IRQ stays high indefinitely.

It seems like the WLAN_IRQ goes low on its own...that it doesn't require any MMC/SDIO transactions to make it go low initially. What could cause the WLAN_IRQ to stay high on initial power up?

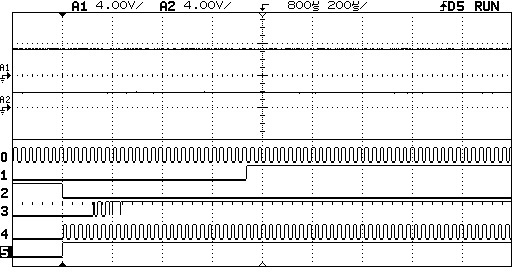

Working Reference Board:

Failing Board: